# SBS 1.1-COMPLIANT GAS GAUGE ENABLED WITH IMPEDANCE TRACK™ TECHNOLOGY FOR USE WITH THE bq29312A

# FEATURES

- Patented Impedance Track<sup>™</sup> Technology Accurately Measures Available Charge in Li-Ion and Li-Polymer Batteries

- Better than 1% Error Over Lifetime of the Battery

- Instant Accuracy No Learning Cycle Required

- Supports the Smart Battery Specification SBS V1.1

- Works With the TI bq29312A Analog Front-End (AFE) Protection IC to Provide Complete Pack Electronics Solution

- Lifetime Data Logging

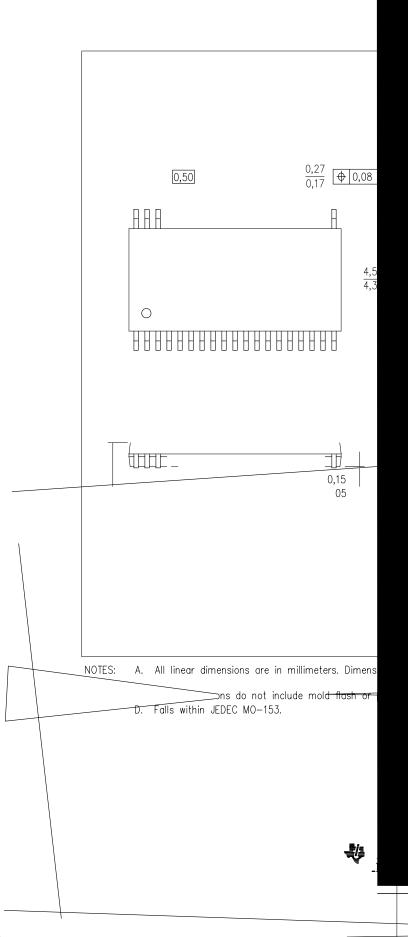

- 38-Pin TSSOP (DBT)

# APPLICATIONS

- Notebook PCs

- Medical and Test Equipment

- Portable Instrumentation

# DESCRIPTION

The bq20z80 SBS-compliant gas gauge IC, incorporating patented Impedance Track<sup>™</sup> technology, is designed for battery-pack or in-system installation. The bq20z80 measures and maintains an accurate record of available **External**

### Components

- Based on a Powerful Low-Power RISC CPU Core With High-Performance Peripherals

- Integrated Field Programmable FLASH Memory Eliminates the Need for External Configuration Memory

- Measures Charge Flow Using a High-Resolution, 16-Bit Integrating Delta-Sigma Converter

- Better Than 0.65 nVh of Resolution

- Self-Calibrating

- Offset Error Less Than 1  $\mu$ V

- Uses 16-Bit Delta-Sigma Converter for Accurate Voltage and Temperature Measurements

- Extensive Data Reporting Options For Improved System Interaction

- Optional Pulse Charging Feature for Improved Charge Times

- Drives 3-, 4- or 5-Segment LED Display for Remaining Capacity Indication

- Supports SHA-1 Authentication

bus. It is designed to work with the bq29312A analog front-end (AFE) protection IC to maximize functionality and safety, and minimize component count and cost in smart battery circuits.

The Impedance Track technology continuously analyzes the battery impedance, resulting in superior gas-gauging accuracy. This enables remaining capacity to be calculated with discharge rate, temperature, and cell aging all accounted for during each stage of every cycle.

### **AVAILABLE OPTIONS**

|                  | PACI                           | KAGE                                |

|------------------|--------------------------------|-------------------------------------|

| T <sub>A</sub>   | 38-PIN TSSOP (DBT)<br>Tube     | 38-PIN TSSOP (DBT)<br>Tape and Reel |

| –40°C to<br>85°C | bq20z80DBT-V102 <sup>(1)</sup> | bq20z80DBTR-V102 <sup>(2)</sup>     |

(1) A single tube quantity is 50 units.

(2) A single reel quantity is 2000 units

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Impedance Track is a trademark of Texas Instruments.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

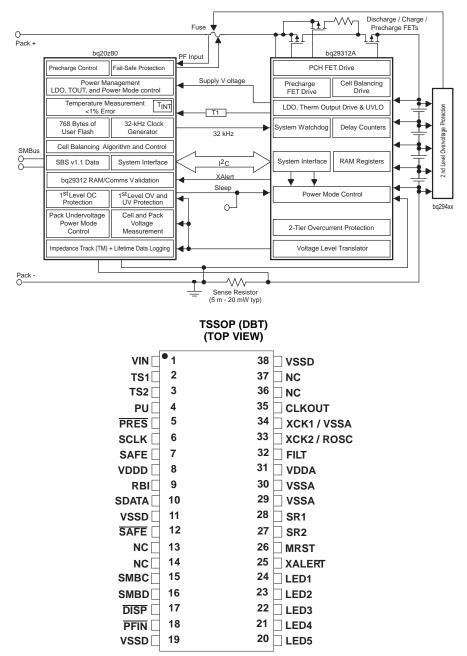

# SYSTEM DIAGRAM

NC - No internal connection

### **TERMINAL FUNCTIONS**

| TER!             | MINAL  | ··(a)(1)           | DESCRIPTION (                                                                                                                                                                    |           |

|------------------|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| NO. NAME   1 VIN |        | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                      |           |

| 1                | VIN    | I                  | Voltage measurement input from the AFE                                                                                                                                           |           |

| 2                | TS1    | I                  | 1 <sup>st</sup> Thermistor voltage input connection to monitor temperature                                                                                                       |           |

| 3                | TS2    | I                  | 2 <sup>nd</sup> Thermistor voltage input connection to monitor temperature                                                                                                       |           |

| 4                | PU     | 0                  | Output to pull up the PRES pin for system detection                                                                                                                              |           |

| 5                | PRES   | I                  | Active low input to sense system insertion and typically requires additional ESD protection                                                                                      |           |

| 6                | SCLK   | I/OD               | Communication clock to the AFE                                                                                                                                                   |           |

| 7                | SAFE   | 0                  | Active high output to enforce additional level of safety protection; e.g., fuse blow. (Inverse of pin 12)                                                                        |           |

| 8                | VDDD   | Р                  | Positive supply for digital circuitry and I/O pins                                                                                                                               |           |

| 9                | RBI    | Р                  | Backup power to the bq20z80 data registers during periods of low operating voltage. RBI accepts a storage capacitor or a battery input.                                          |           |

| 10               | SDATA  | I/O                | Data transfer to and from the AFE                                                                                                                                                |           |

| 12               | SAFE   | 0                  | Active low output to enforce additional level of safety protection; e.g., fuse blow. (Inverse of pin 7)                                                                          |           |

| 13               | NC     | -                  | Not used— leave floating                                                                                                                                                         |           |

| 14               | NC     | -                  | Not used— leave floating                                                                                                                                                         |           |

| 15               | SMBC   | I/OD               | SMBus clock open-drain bidirectional pin used to clock the data transfer to and from the bq20z80                                                                                 |           |

| 16               | SMBD   | I/OD               | SMBus data open-drain bidirectional pin used to transfer address and data to and from the bq20z80                                                                                |           |

| 17               | DISP   | I                  | Display control for the LEDs. This pin is typically connected to bq29312A REG via a 100-k $\Omega$ resistor and a push-button switch to VSSD.                                    |           |

| 18               | PFIN   | I                  | Active low input to detect secondary protector output status and allows the bq20z80 to report the status of the 2 <sup>nd</sup> level protection output                          |           |

| 20               | LED5   | 0                  | LED5 display segment that drives an external LED depending on the firmware configuration                                                                                         |           |

| 21               | LED4   | 0                  | LED4 display segment that drives an external LED depending on the firmware configuration                                                                                         |           |

| 22               | LED3   | 0                  | LED3 display segment that drives an external LED depending on the firmware configuration                                                                                         |           |

| 23               | LED2   | 0                  | LED2 display segment that drives an external LED depending on the firmware configuration                                                                                         |           |

| 24               | LED1   | 0                  | LED1 display segment that drives an external LED depending on the firmware configuration                                                                                         |           |

| 25               | XALERT | I                  | Input from bq29312A XALERT output.                                                                                                                                               |           |

| 26               | MRST   | I                  | Master reset input that forces the device into reset when held high                                                                                                              |           |

| 27               | SR2    | IA                 | Connections for a small-value sense resistor to monitor the battery charge- and discharge-current flow                                                                           |           |

| 28               | SR1    | IA                 | Co.alue the battery charge- and discharge-current                                                                                                                                |           |

| 31               | VDDA   | Р                  | Positive supply for analog circuitry                                                                                                                                             |           |

| 32               | FILT   | IA                 | Analog inputtoexternalfilter components which are a 150-pF capacitor to V <sub>SSA</sub> ,in parj 1el0 0 1 -8 Tf (display18.224 535.6 Tm /F2 -8 Tf (and)Tj 1 0 0 1 333.968 535.6 | Tm /F2 -8 |

|                  |        | <u> </u>           |                                                                                                                                                                                  |           |

| 36, 37           | NC     | -                  | Not used— leave floating                                                                                                                                                         |           |

| 11, 19, 38       | VSSD   | Р                  | Negative supply for digital circuitry                                                                                                                                            |           |

| 29, 30           | VSSA   | Р                  | Negative supply for analog circuitry.                                                                                                                                            |           |

(1) I = Input, IA = Analog input, I/O = Input/output, I/OD = Input/Open-drain

O = Output, OA = Analog output, P = Power

# **ABSOLUTE MAXIMUM RATINGS**

# **ELECTRICAL CHARACTERISTICS**

# bq20z80-V102

SLUS681B-NOVEMBER 2005-REVISED JANUARY 2007

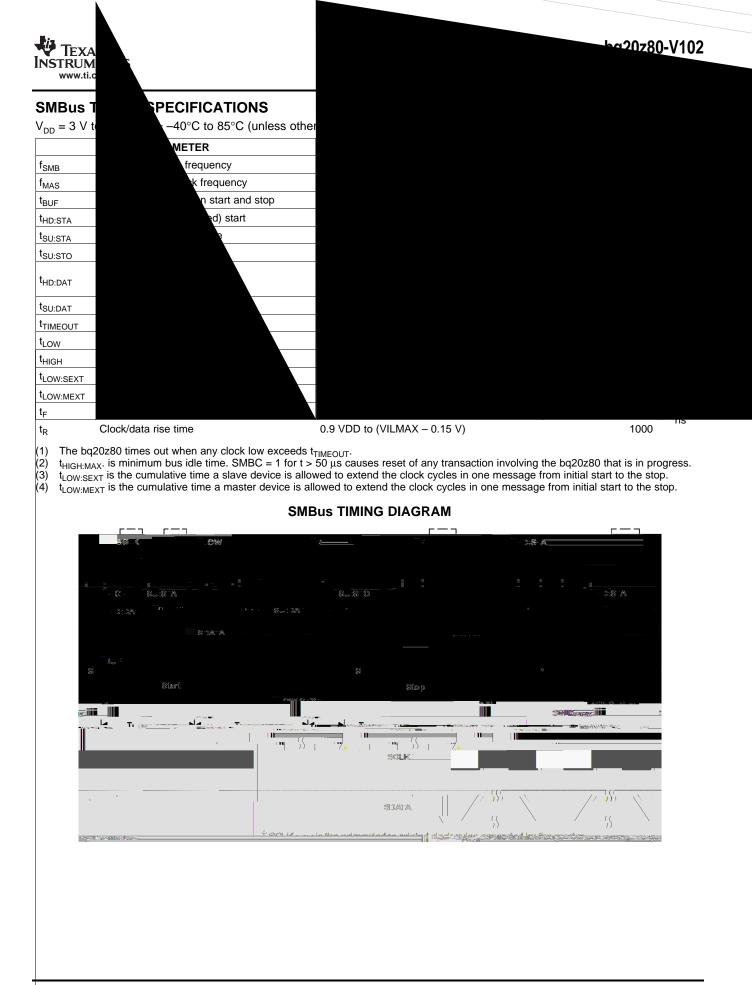

| $V_{DD} = 3$     | 3 V to 3.6 V, $T_A = -40^{\circ}$ C to 85°C (unless otherwise noted) |                 |     |     |     |      |  |

|------------------|----------------------------------------------------------------------|-----------------|-----|-----|-----|------|--|

|                  | PARAMETER                                                            | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |

| V <sub>IT-</sub> | Negative-going voltage input                                         |                 | 2.1 | 2.3 | 2.5 | V    |  |

| $V_{\rm HYS}$    | Power-on reset hysteresis                                            |                 | 50  | 150 | 200 | mV   |  |

### CHARACTERNISTICS(CoulaDDC) INTEGRAT

$V_{DD}$  = 3 V to 3.6 V,  $T_A$  = -40°C to 85°C (unless otherwise noted)

|                     | PARAMETER                                        | TEST CONDITIONS              | MIN   | TYP    | MAX    | UNIT |

|---------------------|--------------------------------------------------|------------------------------|-------|--------|--------|------|

| V <sub>(SR)</sub>   | Input voltage range, $V_{(SR2)}$ and $V_{(SR1)}$ | $V_{(SR)} = V(SR2) - V(SR1)$ | -0.25 |        | 0.25   | V    |

| V <sub>(SROS)</sub> | Input offset                                     |                              |       | 1      |        | μV   |

| INL                 | Integral nonlinearity error                      |                              | Ŭ     | 0.004% | 0.019% |      |

### **CHARACTER**SMITTERSMITTERS

$V_{DD}$  = 3 V to 3.6 V,  $T_A$  = -40°C to 85°C (unless otherwise noted)

|                   | PARAMETER                    | TEST CONDITIONS      | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------|----------------------|-----|-----|-----|------|

| t <sub>(SP)</sub> | Start-up time <sup>(1)</sup> | 0.5% frequency error |     | 2   | 5   | ms   |

(1) The frequency error is measured from the trimmed frequency of the internal system clock which is 128 oscillator frequency, nominally 4.194 MHz.

### OSCILLAT

$V_{\text{DD}}$  = 3 V to 3.6 V,  $T_{\text{A}}$  = –40°C to 85°C (unless otherwise noted)

|                    | PARAMETER                       | TEST CONDITIONS                                 | MIN    | TYP   | MAX   | UNIT |

|--------------------|---------------------------------|-------------------------------------------------|--------|-------|-------|------|

|                    |                                 | ROSC = 100 kΩ                                   | -2%    | 0.25% | 2%    |      |

| f <sub>(exo)</sub> | Frequency error from 32.768 kHz | ROSC = 100 k $\Omega$ , V <sub>DD</sub> = 3.3 V | -1%    | 0.25% | 1%    |      |

|                    |                                 | XCK1 = 12-pF XTAL                               | -0.25% |       | 0.25% |      |

| 4                  | Start up time (1)               | ROSC = 100 kΩ                                   |        |       | 250   | μs   |

| r <sub>(sxo)</sub> | Start-up time <sup>(1)</sup>    | XCK1 = 12-pF XTAL                               |        |       | 200   | ms   |

(1) The start-up time is defined as the time it takes for the oscillator output frequency to be within 1% of the specified frequency.

### DATA FLASH MEMORY CHARACTERISTICS

$V_{\rm DD}$  = 3 V to 3.6 V,  $T_{\rm A}$  = -

# **REGISTER BACKUP**

# FEATURE SET

NOTE:

Primary (1st Level) Safety Features

Secondary (2nd Level) Safety Features

**Charge Control Features**

# FEATURE SET (continued)

### Gas Gauging

The bq20z80 uses the Impedance Track<sup>™</sup> Technology to measure and calculate the available charge in battery cells. The archievable accuracy is better than the coloumb counting method over the lifetime of the battery and there is no full charge discharge learning cycle required.

See Theory and Implementation of Impedance Track Battery Fuel-Gauging Algorithm application note (SLUA364) for further details.

# LED Display

The bq20z80 can drive 3-, 4-, or 5- segment LED display for remaining capacity indication.

# LifeTime Data Logging Features

The bq20z80 offers a lifetime data logging array, where all important measurements are stored for warranty and analysis purposes. The data monitored includes:

- Lifetime maximum temperature

- Lifetime minimum temperature

- Lifetime maximum battery cell voltage

- Lifetime minimum battery cell voltage

- Lifetime maximum battery pack voltage

- Lifetime minimum battery pack voltage

- Lifetime maximum charge current

- Lifetime maximum discharge current

- Lifetime maximum charge power

- Lifetime maximum discharge power

- Lifetime maximum average discharge current

- Lifetime maximum average discharge power

- Lifetime average temperature

#### Authentication

The bq20z80 supports authentication by the host using SHA-1.

### **Power Modes**

The bq20z80 supports 3 different power modes to reduce power consumption:

- In Normal Mode, the bq20z80 performs measurements, calculations, protection decicions, data update in 1 second intervals. Between these intervals, the bq20z80 is in a reduced power stage.

- In Sleep Mode, the bq20z80 performs measurements, calculations, protection decicions, data update in adjustable time intervals. Between these intervals, the bq20z80 is in a reduced power stage.

- In Shutdown Mode the bq20z80 is completety disabled.

### CONFIGURATION

#### **Oscillator Function**

The oscillator of the bq20z80 can be set up for internal or external operation. On power up, the bq20z80 automatically attempts to start the internal oscillator. If a 100-k $\Omega$  resistor is not connected to ROSC (pin 33), then it attempts to start the oscillator using an external 32.768-kHz crystal.

#### NOTE:

Install either the 100-k $\Omega$  ROSC resistor or the 12-pF, 32.768-kHz crystal. Do not install both.

# FEATURE SET (continued)

The performance of the internal oscillator depends on the tolerance of the 100-k $\Omega$  resistor between RSOC (pin 33) and VSSA (pin 34). Choose a resistor with a tolerance of ±0.1%, and 50-ppm or better temperature drift. Place this resistor as close as possible to the bq20z80. If a 12-pF crystal is used, place it as close as possible to the XCK1 (pin 34) and XCK2 (pin 33) pins. If not properly implemented, the PCB layout in this area can degrade oscillator performance.

#### **System Present Operation**

The bq20z80 pulls the PU pin high periodically (1 s). Connect this pin to the PRES pin of the bq20z80 via a resistor of approximately 5 k $\Omega$ . The bq20z80 measures the PRES input during the PU-active period to determine its state. If PRES input is pulled to ground by external system, the bq20z80 detects this as system present.

### **BATTERY PARAMETER MEASUREMENTS**

The bq20z80 uses an integrating delta-sigma analog-to-digital converter (ADC) for current measurement, and a second delta-sigma ADC for individual cell and battery voltage, and temperature measurement.

#### **Charge and Discharge Counting**

The integrating delta-sigma ADC measures the charge/discharge flow of the battery by measuring the voltage drop across a small-value sense resistor between the SR1 and SR2 pins. The integrating ADC measures bipolar signals from -0.25 V to 0.25 V. The bq20z80 detects charge activity when  $V_{SR} = V_{(SR1)}-V_{(SR2)}$  is positive and discharge activity when

Voltage

Current

Auto Calibration

Temperature

COMMUNICATIONS

SMBus On and Off State

1st1st 1st **666(1st**1st

#### SLUS681B-NOVEMBER 2005-REVISED JANUARY 2007

# Table 3. DATAFLASH VALUES (continued)

| Class               | Subclass<br>ID | Subclass    | Offset | Name                        | Data<br>Type | Min Value | Max Value | Default<br>Value | Units |

|---------------------|----------------|-------------|--------|-----------------------------|--------------|-----------|-----------|------------------|-------|

| 1st Level           | 1              | Current     | 0      | OC (1st Tier) Chg           | U2           | 0         | 20000     | 6000             | mA    |

| Safety              |                |             | 2      | OC (1st Tier) Chg Time      | U1           | 0         | 60        | 2                | sec   |

|                     |                |             | 3      | OC Chg Recovery             | 12           | -1000     | 1000      | 200              | mA    |

|                     |                |             | 5      | OC (1st Tister) Dsg         | U2           | 0         | 20000     | 6000             | mA    |

|                     |                |             | 7      | OC (1st Tier) Dsg Time      | U1           | 0         | 60        | 2                | sec   |

|                     |                |             | 8      | OC Dsg Recovery             | U2           | 0         | 1000      | 200              | mA    |

|                     |                |             | 10     | OC (2nd Tier) Chg           | U2           | 0         | 20000     | 8000             | mA    |

|                     |                |             | 12     | OC (2nd Tier) Chg Time      | U1           | 0         | 60        | 2                | Sec   |

|                     |                |             | 13     | OC (2nd Tier) Dsg           | U2           | 0         | 22000     | 8000             | mA    |

|                     |                |             | 15     | OC (2nd Tier) Dsg Time      | U1           | 0         | 60        | 2                | Sec   |

|                     |                |             | 16     | Current Recovery Time       | U1           | 0         | 60        | 8                | Sec   |

|                     |                |             | 17     | AFE OC Dsg                  | H1           | 0x00      | 0x1f      | 0x12             | hex   |

|                     |                |             | 18     | AFE OC Dsg Time             | H1           | 0x00      | 0x0f      | 0x0f             | hex   |

|                     |                |             | 19     | AFE OC Dsg Recovery         | U2           | 10        | 1000      | 100              | mA    |

|                     |                |             | 21     | AFE SC Chg Cfg              | H1           | 0x00      | 0xff      | 0x77             | hex   |

|                     |                |             | 22     | AFE SC Dsg Cfg              | H1           | 0x00      | 0xff      | 0x77             | hex   |

|                     |                |             | 23     | AFE SC Recovery             | U2           | 0         | 200       | 1                | mA    |

| 1st Level           | 2              | Temperature | 0      | Over Temp Chg               | U2           | 0         | 1200      | 550              | 0.1°C |

| Safety              |                |             | 2      | OT Chg Time                 | U1           | 0         | 60        | 2                | Sec   |

|                     |                |             | 3      | OT Chg Recovery             | U2           | 0         | 1200      | 500              | 0.1°C |

|                     |                |             | 5      | Over Temp Dsg               | U2           | 0         | 1200      | 600              | 0.1°C |

|                     |                |             | 7      | OT Dsglstme                 | U1           | 0         | 60        | 2                | Sec   |

|                     |                |             | 8      | OT Dsg Recovery             | U2           | 0         | 1200      | 550              | 0.1°C |

| 1st Level<br>Safety | 3              | Host Comm   | 0      | Host Watchdog Timeout       | U1           | 0         | 255       | 0                | Sec   |

| 2nd Level           | 16             | Voltage     | 0      | SOV Threshold               | U2           | 0         | 20000     | 18000            | mV    |

| Safety              | -              |             | 2      | SOV Time                    | U1           | 0         | 30        | 0                | Sec   |

|                     |                |             | 3      | Cell Imbalance Current      | U1           | 0         | 200       | 5                | mA    |

|                     |                |             | 4      | Cell Imbalance Fail Voltage | U2           | 0         | 5000      | 1000             | mV    |

|                     |                |             | 6      | Cell Imbalance Time         | U1           | 0         | 30        | 0                | Sec   |

|                     |                |             | 7      | Battery Rest Time           | U2           | 0         | 65535     | 1800             | Sec   |

|                     |                |             | 9      | PFIN Detect Time            | U1           | 0         | 30        | 0                | Sec   |

| 2nd Level           | 17             | Current     | 0      | SOC Chg                     | U2           | 0         | 30000     | 10000            | mA    |

| Safety              |                |             | 2      | SOC Chg Time                | U1           | 0         | 30        | 0                | Sec   |

|                     |                |             | 3      | SOC Dsg                     | U2           | 0         | 30000     | 10000            | mA    |

|                     |                |             | 5      | SOC Dsg Time                | U1           | 0         | 30        | 0                | Sec   |

| 2nd Level           | 18             | Temperature | 0      | SOT Chg                     | U2           | 0         |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

|                     |                |             |        |                             |              |           |           |                  |       |

#### SLUS681B-NOVEMBER 2005-REVISED JANUARY 2007

| Class                | Subclass<br>ID | Subclass      | Offset | Name              | Data<br>Type | Min Value | Max Value | Default<br>Value | Unit |

|----------------------|----------------|---------------|--------|-------------------|--------------|-----------|-----------|------------------|------|

| SBS<br>Configuration | 48             | Data          | 0      | Rem Cap Alarm     | U2           | 0         | 700       | 300              | mAh  |

|                      |                |               | 2      | Rem Time Alarm    | U2           | 0         | 30        | 10               | Min  |

|                      |                |               | 4      | Init Battery Mode | H2           | 0x0000    | Oxffff    | 0x0081           | hex  |

|                      |                |               | 6      | Design Voltage    | U2           | 7000      | 18000     | 14400            | mV   |

|                      |                |               | 8      | Spec Info         | H2           | 0x0000    | 0xffff    | 0x0031           | hex  |

|                      |                |               | 10     | Manuf Date        | U2           | 0         | 65355     | 0                | date |

|                      |                |               | 12     | Ser. Num.         | H2           | 0x0000    | Oxffff    | 0x0001           | hex  |

|                      |                |               | Name   | Cycle Count       | U2           | 0         | 65355     | 0                | cnt  |

|                      |                |               | 16     | CC Threshold      | 12           | 100       | 32767     | 4400             | mAh  |

|                      |                |               | 18     | CC %              | U1           | 0         | 100       | 90               | %    |

|                      |                |               | 19     | CF MaxError Limit | U1           | 0         | 100       | 100              | %    |

|                      |                |               | 20     | Design Capacity   | U2           | 0         | 65355     | 4400             | mAh  |

|                      |                |               | 22     | Design Energy     | U2           | 0         | 65355     | 6336             | 10m  |

|                      |                |               | 24     | Manuf Name        | S12          | -         | -         | Texas Inst.      |      |

|                      |                |               | 36     | Device Name       | S8           | -         | -         | bq20z80          |      |

|                      |                |               | 44     | Device Chemistry  | S5           | -         | -         | LION             |      |

| SBS                  | 49             | Configuration | 0      | TDA Set %         | 11           | -1        | 100       | 6                | %    |

| Configuration        | -0             |               | 1      | TDA Clear         |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  | _    |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  | _    |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              |           |           |                  |      |

|                      |                |               |        |                   |              | _         |           |                  | +    |

|                      |                |               |        |                   |              |           |           |                  |      |

# Table 3. DATAFLASH VALUES (continued)

# Table 3. DATAFLASH VALUES (continued)

| Class            | Subclass<br>ID | Subclass              | Offset | Name                    | Data<br>Type | Min Value | Max Value | Default<br>Value | Units |

|------------------|----------------|-----------------------|--------|-------------------------|--------------|-----------|-----------|------------------|-------|

| Configuration 64 | 64             | Registers             | 0      | Operation Cfg A         | H2           | 0x0000    | Oxffff    | 0x0F29           |       |

|                  |                |                       | 2      | Operation Cfg B         | H2           | 0x0000    | Oxffff    | 0x6440           |       |

|                  |                |                       | 4      | Permanent Fail Cfg      | H2           | 0x0000    | 0xffff    | 0x0000           |       |

|                  |                |                       | 6      | Non-Removable Cfg       | H2           | 0x0000    | Oxffff    | 0x0000           | hex   |

| LED Support      | 67             | LED Cfg               | 0      | LED Flash Rate          | U2           | 0         | 65535     | 512              | 500µs |

|                  |                |                       | 2      | LED Blink Rate          | U2           | 0         | 65535     | 1024             | 500µs |

|                  |                |                       | 4      | LED Delay               | U2           | 1         | 65535     | 100              | 500µs |

|                  |                |                       | 6      | LED Hold Time           | U1           | 0         | 255       | 4                | s     |

|                  |                |                       | 7      | CHG Flash Alarm         | l1           | -1        | 101       | 10               | %     |

|                  |                |                       | 8      | CHG Thresh 1            | 11           | -1        | 101       | 0                | %     |

|                  |                |                       | 9      | CHG Thresh 2            | l1           | -1        | 101       | 20               | %     |

|                  |                |                       | 10     | CHG Thresh 3            | 11           | -1        | 101       | 40               | %     |

|                  |                |                       | 11     | CHG Thresh 4            | 11           | -1        | 101       | 60               | %     |

|                  |                |                       | 12     | CHG Thresh 5            | 11           | -1        | 101       | 80               | %     |

|                  |                |                       | 13     | DSG Flash Alarm         | 11           | -1        | 101       | 10               | %     |

|                  |                |                       | 14     | DSG Thresh 1            | 11           | -1        | 101       | 0                | %     |

|                  |                |                       | 15     | DSG Thresh 2            | 11           | -1        | 101       | 20               | %     |

|                  |                |                       | 16     | DSG Thresh 3            | 11           | -1        | 101       | 40               | %     |

|                  |                |                       | 17     | DSG Thresh 4            | 11           | -1        | 101       | 60               | %     |

|                  |                |                       | 18     | DSG Thresh 5            | 11           | -1        | 101       | 60               | %     |

| Power 68         | 68             | Power                 | 0      | Flash Update OK Voltage | U2           | 6000      | 20000     | 7500             | mV    |

|                  |                |                       | 2      | Shutdown Voltage        | U2           | 5000      | 20000     | 7000             | mV    |

|                  |                |                       | 4      | Shutdown Time           | U1           | 0         | 60        | 10               | Sec   |

|                  |                |                       | 5      | Charger Present         | U2           | 0         | 23000     | 12000            | mV    |

|                  |                |                       | 7      | Sleep Current           | U2           | 0         | 100       | 10               | mA    |

|                  |                |                       | 9      | Bus Low Time            | U1           | 0         | 255       | 5                | Sec   |

|                  |                |                       | 10     | Cal Inhibit Temp Low    | 12           | -400      | 1200      | 50               | 0.1°C |

|                  |                |                       | 12     | Cal Inhibit Temp High   | 12           | -400      | 1200      | 450              | 0.1°C |

|                  |                |                       | 14     | Sleep Voltage Time      | U1           | 0         | 100       | 5                | Sec   |

|                  |                |                       | 15     | Sleep Current Time      | U1           | 0         | 255       | 20               | Sec   |

| Gas Gauging      | 80             | IT Cfg                | 0      | Load Select             | U1           | 0         | 255       | 3                | num   |

|                  |                |                       | 1      | Load Mode               | U1           | 0         | 255       | 0                | num   |

|                  |                |                       | 45     | Term Voltage            | 12           | -32768    | 32767     | 12000            | mV    |

|                  |                |                       | 60     | User Rate-mA            | 12           | -9000     | -2000     | 0                | mA    |

|                  |                |                       | 62     | User Rate-mW            | 12           | -14000    | -3000     | 0                | 10mW  |

|                  |                |                       | 64     | Reserve Cap-mAh         | 12           | 0         | 9000      | 0                | mAh   |

|                  |                |                       | 66     | Reserve Cap-mWh         | 12           | 0         | 14000     | 0                | 10mWh |

| Gas Gauging      | 81             | Current<br>Thresholds | 0      | Dsg Current Threshold   | U2           | 0         | 2000      | 100              | mA    |

|                  |                |                       | 2      | Chg Current Threshold   | U2           | 0         | 2000      | 50               | mA    |

|                  |                |                       | 4      | Quit Current            | U2           | 0         | 1000      | 10               | mA    |

|                  |                |                       | 6      | Dsg Relax Time          | U1           | 0         | 255       | 1                | Sec   |

|                  |                |                       | 7      | Chg Relax Time          | U1           | 0         | 255       | 60               | Sec   |

# **Firmware Version Changes**

# bq20z80-V101 to bq20z80-V102 Changes

# Table 4. CHANGE DETAILS

| CHANGE                                                                                                                                                                            | bq0z80-V102                                                                                                                         | bq20z80-V101                                                                                                                                                                                                                                                                                                                    | COMMENTS                                                                                |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| Corrected to allow display to<br>turn off when charging and<br>button pushed.                                                                                                     | LED display operates correctly during charging.                                                                                     | LED display would stay on until<br>charging terminated after the button<br>was pushed. Only occurs when LED<br>display not configured to be always<br>on during charging.                                                                                                                                                       | Correct operation of the LED display under all conditions                               |  |

| Allow negative LED<br>thresholds to permit LED<br>alarms to be disabled                                                                                                           | Configuring negative LED alarm threshold disables LED alarm functionality.                                                          | Feature not available                                                                                                                                                                                                                                                                                                           | Allow better customization                                                              |  |

| Allow zero values for ALARM<br>and CHARGING LED blink<br>rates to disable them                                                                                                    | Configuring zero value for the LED blink rates disables them.                                                                       | Feature not available                                                                                                                                                                                                                                                                                                           | Allow better customization                                                              |  |

| Restore initialization of<br>dodcharge in relaxed state<br>so that the correct dodcharge<br>value is used in capacity<br>estimation                                               | dodcharge initialized to the correct value                                                                                          | dodcharge value set to zero                                                                                                                                                                                                                                                                                                     | Improved gauging accuracy with correct initialization of dodcharge value.               |  |

| Only clear offset calibration<br>flag when SMBus lines go<br>high.                                                                                                                | Prevents offset calibration<br>occurring just because a safety<br>condition occurs and then clears<br>when the SMBus lines are low. | Offset calibration occurs multiple<br>times if safety condition occurs<br>when SMBus lines are low.                                                                                                                                                                                                                             | More appropriate period between<br>offset calibrations when SMBus<br>lines are low.     |  |

| Change so that setting AFE<br>Fail Limit to zero disables<br>PF_AFE_C                                                                                                             | Configurable option to allow<br>disabling PF_AFE_C trigger                                                                          | Feature not available.                                                                                                                                                                                                                                                                                                          | Allow better customization                                                              |  |

| Enable LED display to turn<br>off after charge termination<br>and if SMBus lines are<br>detected low and LEDs<br>enabled during charging.                                         | LED display turns off after charge termination.                                                                                     | LED display stays on when charging terminates after SMBus lines are detected low.                                                                                                                                                                                                                                               | Correct operation of the LED display under all conditions                               |  |

| Set charge FET state<br>immediately when entering<br>sleep                                                                                                                        | Charge FET state set correctly,<br>immediately after entering sleep                                                                 | The CHG FET would not get set to<br>the correct state for sleep until the<br>first voltage measurement.                                                                                                                                                                                                                         | Quicker transition of FET to the correct state in sleep                                 |  |

| Change DF:Operation Cfg B<br>[CCT = 0], so that<br>SBS.CycleCount() threshold<br>is in mAH, not in % of FCC                                                                       | Data flash default bases<br>SBS.CycleCount() calculation on<br>mAh and not % of FCC                                                 | DF:Operation Cfg B [CCT = 1],<br>making the default<br>SBS.CycleCount() calculation to be<br>based on % of FCC                                                                                                                                                                                                                  | Data flash default changed to reflect common customer usage                             |  |

| When DF:Operation Cfg B<br>[CCT = 1], so that<br>SBS.CycleCount() threshold<br>is % of FCC, then DF:CC<br>Threshold is used as a<br>minimum for the<br>SBS.CycleCount() threshold | Use <i>DF:CC Threshold</i> as the minimum to prevent rapid incrementing of the <i>SBS.Cyclecount()</i> , damaging the data flash    | Small or negative SBS.Full Charge<br>Capacity() values (should not occur<br>under normal operation) from<br>causing the SBS.CycleCount()<br>incrementing rapidly, potentially<br>damaging the data flash                                                                                                                        | Improved system reliability                                                             |  |

| When exiting the relaxed<br>state to sleep, the initial<br>charge capacity is correctly<br>calculated                                                                             | Corrected initial charge capacity<br>calculation to be accurate when<br>exiting relaxed state to sleep                              | If the relaxed state was exited to<br>sleep after a valid DOD<br>measurement (30-minute default<br>value), then the initial charge<br>capacity would not be recalculated<br>and would result in an incorrect FCC<br>value if the sleep state was exited<br>before another valid DOD<br>measurement (30-minute default<br>value) | More reliable<br>SBS:FullChargeCapacity()<br>calculation under all system<br>conditions |  |

# Table 4. CHANGE DETAILS (continued)

| CHANGE                                                                                                                                                                                                                                                                                                                                                            | bq0z80-V102                                                                                  | bq20z80-V101                                                                                                                                                                                                                                                                                                                                              | COMMENTS                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Correct update of Remcap in<br>relaxed state to use passed<br>charge                                                                                                                                                                                                                                                                                              | Charge or discharge current<br>accumulated in a relaxed state<br>used to update Remcap       | If the relaxed state was exited after<br>the accumulation of significant<br>charge or discharge current (over at<br>most 100 seconds with default<br>values), the RemCap and FCC<br>would be in error by this charge.<br>This is only significant if the relaxed<br>state can exist with significant<br>current as determined by application<br>settings. | More reliable<br>SBS:FullChargeCapacity()<br>SBS:RemainingCapacity()<br>calculation under all system<br>conditions |

| Implement disable of<br>resistance update based on<br>accumulative scale. If the<br>product of 15 consecutive<br>(default value) resistance<br>scale factors is less than 0.5<br>or more than 1.5, then<br>resistance update is disabled<br>until the next valid soc<br>measurement. Sets bit 2 of<br>Operation Status to indicate<br>resistance update disabled. | Prevent invalid soc values from<br>causing incorrect resistance<br>updates                   | Incorrect resistance updates that<br>could result from invalid soc values                                                                                                                                                                                                                                                                                 | More reliable resistance updates<br>under all system conditions                                                    |

| Implement disable of<br>resistance update based on<br>estimated capacity error.<br>Sets bit 2 of Operation Status<br>to indicate resistance update<br>disabled.                                                                                                                                                                                                   | Prevent invalid soc values from causing incorrect resistance updates                         | Incorrect resistance updates that could result from invalid soc values                                                                                                                                                                                                                                                                                    | More reliable resistance updates<br>under all system conditions                                                    |

| Disable Qmax increment if due to Grid 14 and exit of discharge                                                                                                                                                                                                                                                                                                    | Prevent unnecessary Qmax increments                                                          | Qmax increments can occur due to Grid 14 and exit of discharge                                                                                                                                                                                                                                                                                            | Improved Qmax data reliability under all system conditions.                                                        |

| Drive all unused pins low                                                                                                                                                                                                                                                                                                                                         | Provides better ESD immunity                                                                 | Not all unused pins driven low                                                                                                                                                                                                                                                                                                                            | Improved ESD immunity                                                                                              |

| Initial charge capacity<br>calculation when dod0 is<br>measured in the<br>overdischarged state is<br>corrected                                                                                                                                                                                                                                                    | Overdischarged state does not<br>affect the accuracy of FCC<br>calculations                  | An incorrect initial charge capacity<br>affects FCC that is calculated during<br>discharge or a Qmax update. If FCC<br>is not changed by a Qmax update,<br>then reported RemainingCapacity<br>could be negative after 5 hours of<br>relaxation                                                                                                            | More reliable<br>SBS:FullChargeCapacity()<br>SBS:RemainingCapacity()<br>calculation under all system<br>conditions |

| Correct calculation of FCC<br>and RemCap when dod0 is<br>taken when the battery is<br>overdischarged or<br>overcharged. This allows<br>RemCap to go negative, or<br>greater than FCC (though is<br>only reported from 0 - FCC).                                                                                                                                   | Overcharged/Overdischarged<br>does not affect the accuracy of<br>FCC and RemCap calculations | The RemainingCapacity will<br>increment (or decrement) during<br>charging (discharging) even when<br>the battery is in an overdischarged<br>(overcharged) state.                                                                                                                                                                                          | More reliable<br>SBS:FullChargeCapacity()<br>SBS:RemainingCapacity()<br>calculation under all system<br>conditions |

| Change cell imbalance<br><i>DF:Battery Rest Time</i> from 1<br>byte to 2 bytes and set the<br>default value to 1800<br>seconds                                                                                                                                                                                                                                    | New feature providing improved customization                                                 | Feature not available                                                                                                                                                                                                                                                                                                                                     | Improved customization for Cell<br>Imbalance detection                                                             |

| Use upper and lower limit for resistance accumulative scale. Set default values to 300% and 30%.                                                                                                                                                                                                                                                                  |                                                                                              |                                                                                                                                                                                                                                                                                                                                                           | More reliable resistance updates<br>under all system conditions                                                    |

| Add <i>DF:CF MaxError limit</i> for<br>setting <i>SBS.BatteryMode()</i><br>[ <i>CONDITION FLAG</i> ]. Set<br>default value to 100%.                                                                                                                                                                                                                               | New feature providing improved customization                                                 | Feature not available                                                                                                                                                                                                                                                                                                                                     | Improved customization                                                                                             |

# bq20z80-V102

### SLUS681B-NOVEMBER 2005-REVISED JANUARY 2007

| CHANGE                                                                   | bq20z80                                                                               | bq20z80-V101                                                                                           | COMMENTS                                                       |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| nproved thermal model                                                    | A preliminary thermal mode was used.                                                  | An updated thermal model is used.                                                                      | Improved thermal compensation of<br>Impedance Track™ algorithm |

| nproved cell capacity measurement<br>y limiting valid temperature ranges | Valid voltage measurements for cell capacity estimation can occur at any temperature. | Valid voltage measurements for cell capacity estimation must occur within a defined temperature range. | Improves capacity estimation                                   |

| nproved cell capacity measurement                                        |                                                                                       | 29 142.4 TTf (cell)Tj 1 0 0 1.6 8Tf (Impro                                                             | ved)Tj 1726.9 681   f 0 0 0 rg 31310 1 53                      |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

|                                                                          |                                                                                       |                                                                                                        |                                                                |

### **PACKAGING INFORMATION**

| Orderable Device   | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|--------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| BQ20Z80DBT-V102    | NRND                  | TSSOP           | DBT                | 38   | 50             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| BQ20Z80DBTR-V102   | NRND                  | TSSOP           | DBT                | 38   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| BQ20Z80DBTR-V102G4 | NRND                  | TSSOP           | DBT                | 38   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| BQ20ZDBT-V102G4    | NRND                  | TSSOP           | DBT                | 38   | 50             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |