Data Sheet December 17, 2007 FN6626.0

## High Power LED Driver

The ISL78100 is a high-power LED backlight driver with an integrated 36V FET designed to drive up to 8 high-power LEDs in series. The PWM converter runs from an internally generated 1MHz clock. With efficiencies over 90%, the regulator provides tight control of LED current and may be configured in either boost or buck topologies, allowing from 3 to 8 series diodes to be driven from wide input voltages.

LED light level may be controlled either by:

- 1. LED DC bias current set via the LEVEL pin, or

- 2. External low frequency PWM control via the ENABLE/PWM pin.

In both control modes, optional over-temperature thermal protection of the LED reduces the LED DC bias current above an adjustable set temperature, protecting the LED from thermal damage. An optional fault monitor drives an external FET between the input supply and inductor, providing short circuit current protection for the LED and inductor as well as load dump protection for automotive applications. For low cost applications the pass transistor may be omitted and the fault pin bypassed.

The ISL78100 is packaged in a 20 Ld 4mmx4mm QFN package and is specified for operation over the -40°C to +105°C temperature range.

## **Ordering Information**

| PART<br>NUMBER<br>(Note) | PART<br>MARKING | PACKAGE<br>(Pb-free)           | PKG.<br>DWG.# |

|--------------------------|-----------------|--------------------------------|---------------|

| ISL78100ARZ              | 781 00ARZ       | 20 Ld 4x4 QFN                  | L20.4x4C      |

| ISL78100ARZ-TK*          | 781 00ARZ       | 20 Ld 4x4 QFN<br>Tape and Reel | L20.4x4C      |

| ISL78100ARZ-T*           | 781 00ARZ       | 20 Ld 4x4 QFN<br>Tape and Reel | L20.4x4C      |

\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **Features**

- Drives 3 to 8 high-power LEDs in series, up to 32V

- 2.7V to 16V input voltage range

- · Boost or Buck configurable switch

- · 3A integrated FET

- · Automotive load dump protection

- · Light output temperature compensation

- · LED over-temperature protection

- LED disconnect

- · PWM/analog light level control

- Small, 20 Ld 4mmx4mm QFN package

- TS-16949 and AEC-Q100 Compliant

- Pb-free (RoHS compliant)

## **Applications**

- · Automotive display backlighting

- · Automotive LED lighting

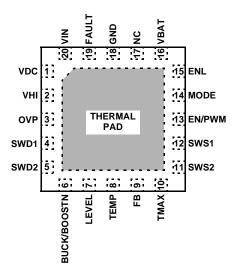

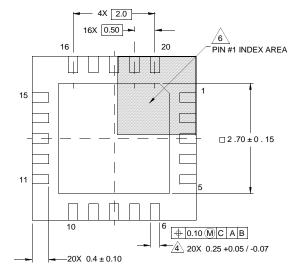

#### **Pinout**

ISL78100 (20 LD 4X4 QFN) TOP VIEW

## **Absolute Maximum Ratings** $(T_A = +25^{\circ}C)$

| Maximum pin voltage, all pins except below 6.5V |      |

|-------------------------------------------------|------|

| VIN SWS1, SWS2, EN/PWM                          | 18V  |

| VBÅT, FAULT, FB                                 | 24V  |

| VHI - SWS1, SWS2                                | 3.5V |

| SWD1, SWD2, OVP                                 | 34V  |

| Continuous Output Current                       | .1A  |

#### **Thermal Information**

| Thermal Resistance                      | $\theta_{\sf JA}$ (°C/W) / | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------|----------------------------|------------------------|

| 20 Ld QFN Package (Notes 1, 2)          | 39                         | 2.5                    |

| Maximum Junction Temperature            |                            | +135°C                 |

| Storage Temperature                     | 65°                        | C to +150°C            |

| Pb-free reflow profile                  | se                         | e link below           |

| http://www.intersil.com/pbfree/Pb-FreeF | Reflow.asp                 |                        |

#### **Operating Conditions**

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

## NOTES:

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{\mbox{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

## $\textbf{Electrical Specifications} \qquad V_{BAT} = V_{IN} = 12V, \ V_{DC} = 5V, \ T_{A} = -40^{\circ}C \ \text{to } +105^{\circ}C \ \text{unless otherwise specified}.$

| PARAMETER                      | DESCRIPTION                                          | CONDITIONS                                                                      | MIN  | TYP  | MAX   | UNIT |

|--------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------|------|------|-------|------|

| VIN                            | Input Supply Voltage                                 | I <sub>OUT</sub> = 350mA, 8 LEDs, BUCK/BOOSTN = GND                             | 5    |      | 16    | V    |

| VIN                            | Input Supply Voltage                                 | I <sub>OUT</sub> = 350mA, 5 LEDs, BUCK/BOOSTN = GND, TMAX disabled              | 2.7  |      | 12    | V    |

| V <sub>BAT</sub>               | Input Supply Monitor                                 | Normal operating range                                                          | 2.7  |      | 16    | V    |

| V <sub>BATFAULT</sub>          | Supply Fault Threshold                               | If V <sub>BAT</sub> > V <sub>BATFAULT</sub> , FAULT pin is switched to ground   | 17.6 | 21   | 24    | V    |

| I <sub>S</sub> E <sub>N</sub>  | Supply Current in V <sub>IN</sub>                    | No switching, EN/PWM = 1                                                        |      | 2.7  | 3.5   | mA   |

| I <sub>S</sub> D <sub>IS</sub> | Supply Current in V <sub>IN</sub>                    | No switching, EN/PWM = 0                                                        |      | 0.6  | 2.5   | μΑ   |

| R <sub>SWITCH</sub>            | Power FET On-Resistance                              | I <sub>SWITCH</sub> = 600mA                                                     |      | 0.15 | 0.25  | Ω    |

| V <sub>DC</sub>                | Regulated Auxiliary Supply                           |                                                                                 | 4.75 | 5    | 5.25  | V    |

| R <sub>OUTOL</sub>             | Auxiliary Supply Open Loop Output<br>Resistance      | V <sub>IN</sub> < V <sub>DC</sub>                                               |      |      | 40    | Ω    |

| R <sub>OUTCL</sub>             | Auxiliary Supply Closed Loop Output Resistance       | V <sub>IN</sub> > 6V, F < 100Hz                                                 |      |      | 6.5   | Ω    |

| lout                           | Output Drive Current                                 | 4 LED output string. V <sub>IN</sub> = V <sub>BAT</sub> = 10V                   |      | 1    |       | Α    |

| I <sub>LIMBOOST</sub>          | Power Switch Current Limit                           | BUCK/BOOSTN = GND                                                               |      | 3.6  |       | Α    |

| ILIMBUCK                       | Power Switch Current Limit                           | BUCK/BOOSTN = VDC                                                               |      | 2.4  |       | Α    |

| OVPH                           | Overvoltage Positive Going Voltage<br>Mode Threshold | Upper threshold to enter overvoltage fault mode, $T_A = +25^{\circ}C$           | 31   | 32   |       | V    |

| OVPL                           | Overvoltage Negative Going Voltage<br>Mode Threshold | Lower threshold to exit overvoltage fault mode, T <sub>A</sub> = +25°C          |      | 20   | 23    | V    |

| V <sub>GATE</sub>              | Protection FET VGS (Gate Clamp)                      | V <sub>IN</sub> - V <sub>FAULT</sub>                                            | 9.76 | 12.2 | 14.64 | V    |

| V <sub>GATE</sub>              | Protection FET VGS (Gate Clamp)                      | V <sub>FAULT</sub> - V <sub>IN</sub>                                            | 8.16 | 10.2 | 12.24 | V    |

| $V_{FB}$                       | Feedback Voltage                                     | System in regulation, V <sub>LEVEL</sub> = 1V,<br>V <sub>IN</sub> = 12V, 6 LEDs | 0.18 | 0.2  | 0.22  | V    |

| V <sub>LEVEL</sub>             | Light Control Voltage Linear Input<br>Range          | Mode = 1, analog control of LED current                                         | 0.25 |      | 3     | V    |

| FB <sub>UV FAULT</sub>         | Feedback Undervoltage Fault                          | V <sub>LEVEL</sub> = 1V, EN/PWM = 3V                                            | 100  | 160  | 200   | mV   |

# **Electrical Specifications** $V_{BAT} = V_{IN} = 12V$ , $V_{DC} = 5V$ , $T_{A} = -40^{\circ}$ C to +105°C unless otherwise specified. **(Continued)**

| PARAMETER              | DESCRIPTION                                                           | CONDITIONS                                    | MIN                 | TYP  | MAX                | UNIT |

|------------------------|-----------------------------------------------------------------------|-----------------------------------------------|---------------------|------|--------------------|------|

| FB <sub>OV</sub> FAULT | Feedback Overvoltage Fault                                            | V <sub>LEVEL</sub> = 1V, EN/PWM = 3V          | 220                 | 250  | 300                | mV   |

| f <sub>SW</sub>        | Switching Frequency                                                   |                                               | 800                 | 1000 | 1150               | kHz  |

| f <sub>DIMMING</sub>   | Maximum Recommended PWM Dimming Frequency                             | Mode = 1, modulation signal applied to EN/PWM |                     | 10   |                    | kHz  |

| <sup>t</sup> SWITCH    | Load Switch Transition Time                                           | C <sub>GATE</sub> = 2nF                       |                     | 100  |                    | ns   |

| RLS <sub>DRIVERL</sub> | Load Switch Driver Impedance Low                                      | EN/PWM = 0                                    |                     | 30   | 50                 | Ω    |

| RLS <sub>DRIVERH</sub> | Load Switch Driver Impedance High                                     | EN/PWM = 3V                                   |                     | 30   | 52                 | Ω    |

| t <sub>FAULT</sub>     | Fault Timer Period                                                    |                                               | 40                  | 50   | 60                 | ms   |

| <sup>t</sup> DELAY     | Start-up Delay                                                        | Timed LX switching delay                      | 0.85                | 1    | 1.24               | ms   |

| V <sub>FAULTPUMP</sub> | Fault Pin Charge Pump                                                 | V <sub>BAT</sub> = V <sub>IN</sub> = 3V       | 6                   |      |                    | V    |

| V <sub>BOOST</sub>     | Boost Mode Threshold                                                  | BUCK/BOOSTN = GND                             |                     |      | 0.4V <sub>DC</sub> | V    |

| V <sub>BUCK</sub>      | Buck Mode Threshold                                                   | BUCK/BOOSTN = V <sub>DC</sub>                 | 0.94V <sub>DC</sub> |      |                    | V    |

| V <sub>MODEL</sub>     | Mode Low Threshold                                                    | MODE = GND                                    |                     |      | 1/3V <sub>DC</sub> | V    |

| V <sub>MODEH</sub>     | Mode High Threshold                                                   | MODE = V <sub>DC</sub>                        | 2/3V <sub>DC</sub>  |      |                    | V    |

| en <sub>FAULT</sub>    | Input Level Applied to TMAX Pin to<br>Enable Fault Protection         |                                               |                     |      | 0.9V <sub>DC</sub> | ٧    |

| dis <sub>FAULT</sub>   | Input Level Applied to TMAX Pin to Disable Fault Protection           |                                               | 0.96V <sub>DC</sub> |      |                    | V    |

| en <sub>TEMP</sub>     | Input Level Applied to TEMP Pin to<br>Enable Temperature Compensation |                                               | 0.5                 |      |                    | ٧    |

| dis <sub>TEMP</sub>    | Input Level Applied to TEMP Pin to Disable Temperature Compensation   |                                               |                     |      | 0.08               | ٧    |

| T <sub>COMPP</sub>     | VFB Positive Temperature<br>Compensation; VFB/VFBnom                  | VTEMP/VDC = 0.80                              |                     | 1.26 |                    |      |

| T <sub>COMPN</sub>     | VFB Negative Temperature<br>Compensation; VFB/VFBnom                  | VTEMP/VDC = 0.20                              |                     | 0.74 |                    |      |

| T <sub>TRIP</sub>      | Internal Temperature Protection<br>Threshold                          |                                               |                     | 135  |                    | °C   |

| T <sub>HYS</sub>       | Internal Temperature Protection<br>Hysteresis                         |                                               |                     | 25   |                    | °C   |

| VEN/PWM <sub>L</sub>   | EN/PWM Pin Input Low Threshold                                        |                                               |                     |      | 1.2                | V    |

| VEN/PWM <sub>H</sub>   | EN/PWM Pin Input High Threshold                                       |                                               | 2.5                 |      |                    | V    |

| V <sub>DCUVLO</sub>    | V <sub>DC</sub> Undervoltage Lockout                                  |                                               |                     |      | 2.6                | V    |

| R <sub>Schottky</sub>  | Internal Schottky Diode for Buck                                      |                                               |                     | 15   | 23                 | Ω    |

## TABLE 1. LIGHT OUTPUT CONTROL, $V_{DC} = 5.0V$

| MODE       | TEMP             | OPERATING MODE                                                                                                               |

|------------|------------------|------------------------------------------------------------------------------------------------------------------------------|

| 1          | ,                | <b>Standard Mode</b> light level to PWM modulation of EN/PWM input; LED bias current determined by LEVEL voltage, nominal 1V |

| Don't Care | V < 0.25V        | Disable temperature compensation                                                                                             |

| 0          | V < (VDC - 0.25) | Fixed Bias Mode V <sub>FB</sub> level internally set to 0.4V, independent of V <sub>LEVEL</sub>                              |

100

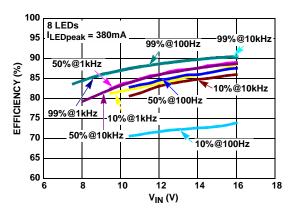

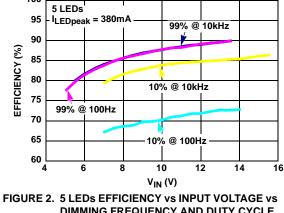

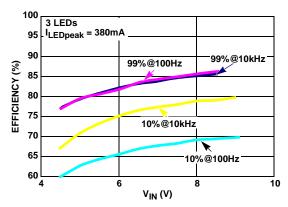

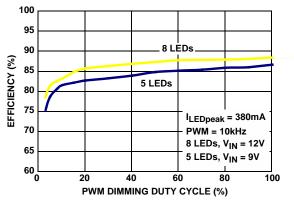

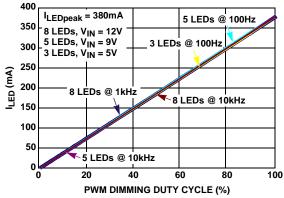

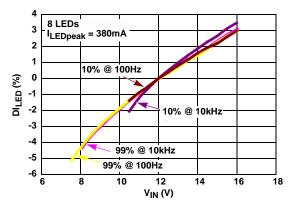

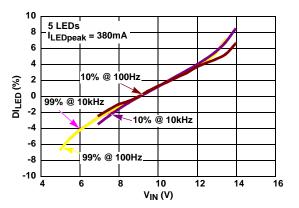

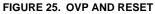

## **Typical Performance Curves**

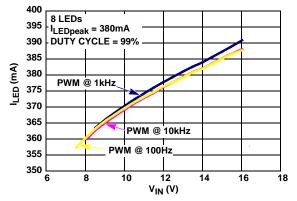

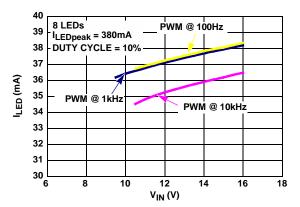

FIGURE 1. 8 LEDs EFFICIENCY vs INPUT VOLTAGE vs **DIMMING FREQUENCY AND DUTY CYCLE**

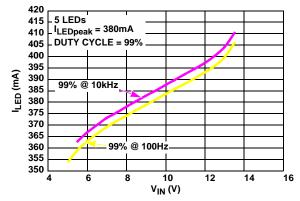

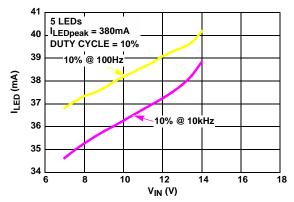

DIMMING FREQUENCY AND DUTY CYCLE

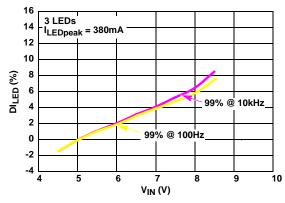

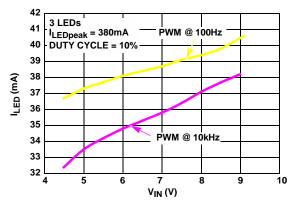

FIGURE 3. 3 LEDs EFFICIENCY vs INPUT VOLTAGE vs **DIMMING FREQUENCY AND DUTY CYCLE**

FIGURE 4. 8 AND 5 LEDs EFFICIENCY vs PWM DUTY CYCLE

FIGURE 5. LEDs PWM DIMMING LINEARITY

FIGURE 6. 8 LEDS CURRENT ACCURACY vs INPUT VOLTAGE

FIGURE 7. 5 LEDS CURRENT ACCURACY VS INPUT VOLTAGE

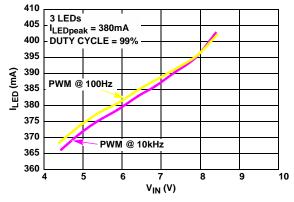

FIGURE 8. 3 LEDs CURRENT ACCURACY vs INPUT VOLTAGE

FIGURE 9. 8 LEDs LINE REGULATION OF PWM DUTY CYCLE OF 99%

FIGURE 10. 5 LEDs LINE REGULATION OF PWM DUTY CYCLE OF 99%

FIGURE 11. 3 LEDs LINE REGULATION OF PWM DUTY CYCLE OF 99%

FIGURE 12. 8 LEDs LINE REGULATION OF PWM DUTY **CYCLE OF 10%**

5

FIGURE 13. 5 LEDs LINE REGULATION OF PWM DUTY CYCLE OF 10%

FIGURE 14. 3 LEDs LINE REGULATION OF PWM DUTY CYCLE OF 10%

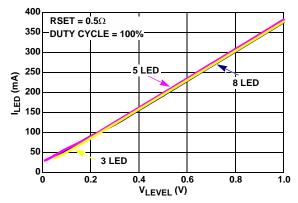

FIGURE 15. LED CURRENT vs V<sub>LEVEL</sub> BIAS

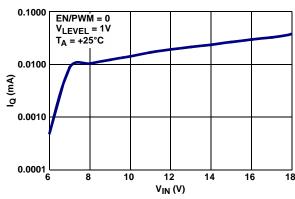

FIGURE 16. QUIESCENT CURRENT (NON-SWITCHING)

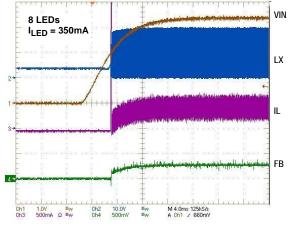

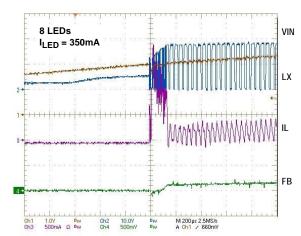

FIGURE 17. START-UP WAVEFORMS

FIGURE 18. START-UP WAVEFORMS ZOOM-IN

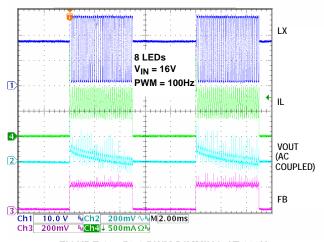

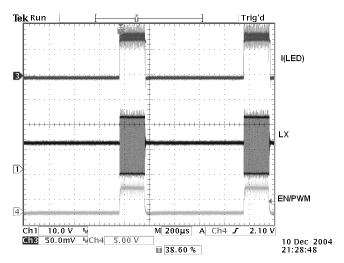

FIGURE 19. 50% PWM DIMMING AT 100Hz

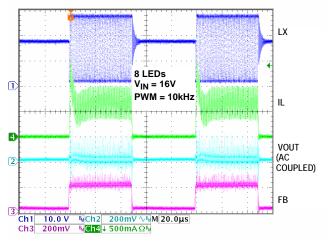

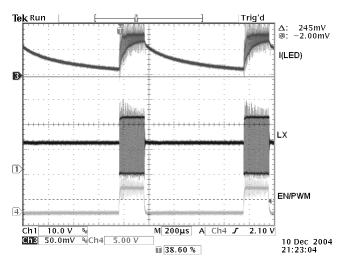

FIGURE 20. 50% PWM DIMMING AT 10kHz

FIGURE 21. 10% PWM DIMMING AT 1kHz

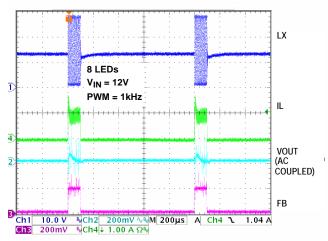

FIGURE 22. 50% PWM DIMMING AT 1kHz ZOOM-IN

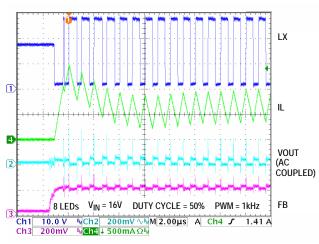

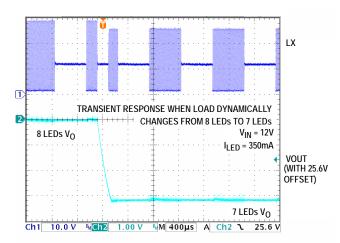

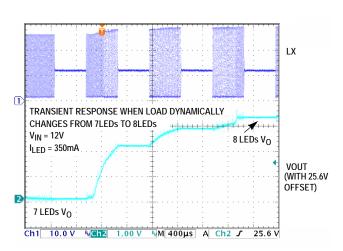

FIGURE 23. TRANSIENT RESPONSE OPERATES FROM 8 TO 7 LEDs

FIGURE 24. TRANSIENT RESPONSE OPERATES FROM 7 TO 8 LEDs

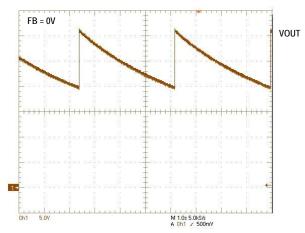

FIGURE 26. CURRENT LIMIT

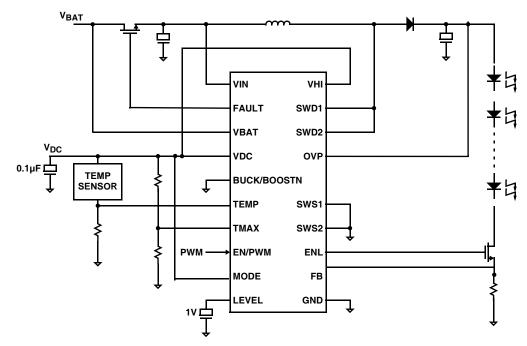

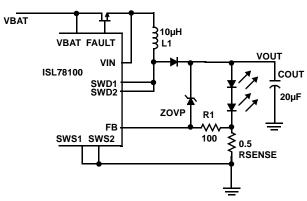

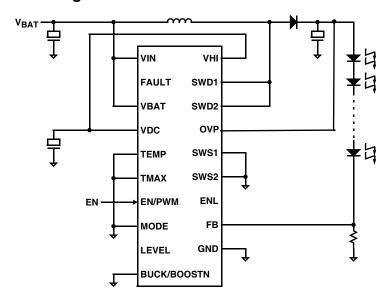

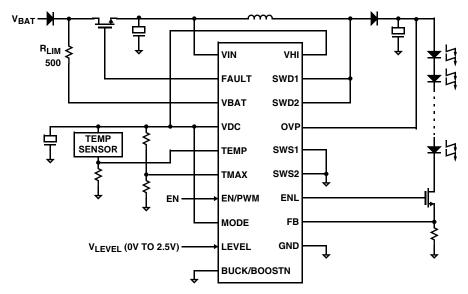

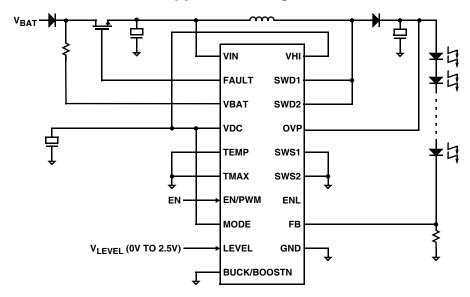

# Typical Boost Mode Application Diagram

FIGURE 27. TYPICAL BOOST MODE APPLICATION CIRCUIT

# Pin Descriptions

| PIN | NAME        | DESCRIPTION                                                                                                                                                                                                                    |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDC         | Internally regulated 5V supply, tracks $V_{IN}$ for input voltages less than 5V. LDO output can also be biased with external supply if $V_{IN}$ is <5.5V. A minimum of 3.3 $\mu$ F decoupling capacitor is needed in this pin. |

| 2   | VHI         | Power FET gate drive supply. Can be biased with external supply if V <sub>IN</sub> is <5.5V                                                                                                                                    |

| 3   | OVP         | Overvoltage monitor input; tie to VOUT for normal operation                                                                                                                                                                    |

| 4   | SWD1        | NMOS power FET drain                                                                                                                                                                                                           |

| 5   | SWD2        | NMOS power FET drain                                                                                                                                                                                                           |

| 6   | BUCK/BOOSTN | Tie to GND for BOOST operation and to VDC for Buck operation                                                                                                                                                                   |

| 7   | LEVEL       | Sets LED bias current level; VFB(nominal) = VLEVEL/5                                                                                                                                                                           |

| 8   | TEMP        | Temperature reference, tie to GND to disable temperature compensation                                                                                                                                                          |

| 9   | FB          | LED current feedback                                                                                                                                                                                                           |

| 10  | TMAX        | Maximum LED temperature set point; if TEMP voltage exceeds TMAX, FB set point will be reduced                                                                                                                                  |

| 11  | SWS2        | NMOS power FET source                                                                                                                                                                                                          |

| 12  | SWS1        | NMOS power FET source                                                                                                                                                                                                          |

| 13  | EN/PWM      | Chip enable and light modulation PWM dimming input                                                                                                                                                                             |

| 14  | MODE        | Digital Input; tie to GND to set FB reference to 400mV, tie to VDC to control FB reference with LEVEL input                                                                                                                    |

| 15  | ENL         | LED load isolation MOS gate driver                                                                                                                                                                                             |

| 16  | VBAT        | Input supply monitor                                                                                                                                                                                                           |

| 17  | NC          | Leave floating (internally connected)                                                                                                                                                                                          |

| 18  | GND         | Ground return and FB ground reference                                                                                                                                                                                          |

| 19  | FAULT       | Gate drive of fault protection FET. Driven low under fault conditions                                                                                                                                                          |

| 20  | VIN         | Input supply                                                                                                                                                                                                                   |

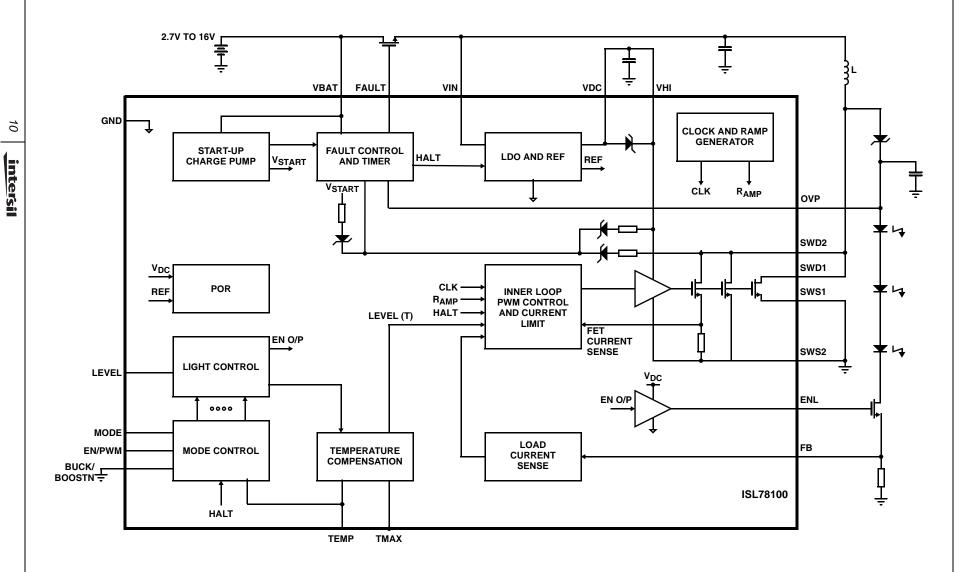

FIGURE 28. ISL78100 BLOCK DIAGRAM

## Theory of Operation

#### **General Description**

The ISL78100 is a flexible, highly integrated high-power LED driver consisting of a PWM switching controller and integrated 36V NDMOS power FET. The device can drive up to 8 series high-power LED's at currents up to 1A at 16V input or 5 LEDs at current up to 350mA at 2.7V input. The control loop can be configured as either a boost or buck regulator with the configuration of the BUCK/BOOSTN pin, providing an output voltage above or below the input supply voltage, depending on the number of stacked LEDs. The controller operates from 2.7V to 16V depending on the numbers of LEDs and current required and can be powered by a single lithium ion battery, 5V or 12V regulated supplies or automotive electrical systems. LED current is sensed through a low value resistor in series with the LED. A thermistor can be used to implement a thermal protection scheme to limit the maximum LED temperature to a preset desirable level.

## Switching Regulator

The ISL78100 employs a current mode PWM control scheme with a nominal switching frequency of 1MHz. This provides fast transient response and enables the use of low profile inductors and compact multilayer ceramic capacitors. Settling time is optimized by the use of a simple control loop without an error amplifier, relying instead on intrinsic gain within the direct summing path. Due to the lower loop gain, offset must be accounted for when setting up initial LED bias current. Refer to the "Application Configurations" on page 11 of the datasheet for further information. Figure 28 shows a block diagram of the system.

## Application Configurations

## **Operating Modes**

The ISL78100 can operate as either a buck or boost regulator. Hardwire BUCK/BOOSTN to GND for boost mode or to VDC for buck mode. In buck mode the power NDMOS drive circuit is "floated" (boot-strapped) allowing the NDMOS gate to be driven above VIN to fully enhance the power NDMOS. An internal Schottky diode between VDC (5V) and VHI reduces external component count. Use a ceramic capacitor of at least 50nF between VHI and SWS1/2 to bootstrap VHI.

#### **LED Load Connection**

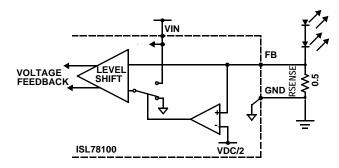

ISL78100 includes an auto-sensing FB level shift circuit that enables the LED load to be connected to either GND or VIN. An internal sense circuit monitors the FB pin voltage. When the level exceeds VDC/2, the feedback reference voltage is switched from GND to VIN. Refer to the application section of the datasheet for typical application schematics.

FIGURE 29. FB REFERENCE AUTO SWITCH

#### Start-up

To maximize external PWM switching speed, the ISL78100 does not include an internal soft-start circuit. When VDC exceeds the power-on reset threshold, switching is delayed for 1ms (t<sub>DELAY</sub>) allowing the output capacitor to charge through the inductor. If soft-start control is required, a suitable application circuit is shown in Figure 30.

FIGURE 30. EXTERNAL SOFT-START CIRCUIT

#### **Light Level Control**

Two light control schemes are provided:

- An external PWM signal via the EN/PWM pin, providing low frequency PWM dimming.

- Bias current level adjustment via the LEVEL input or fixed internal bias.

### **PWM Dimming**

LED color temperature varies with bias current. In backlighting applications, PWM dimming offers better control of color temperature because current through the LEDs is kept constant. A 5V gate driver (ENL) synchronized to EN/PWM can be used to control an external N-Channel FET and disconnect the LED stack during the PWM off-period. The switch prevents discharge of the output capacitor by the LED load, maintaining a constant bias independent of PWM duty cycle. Operation at 1kHz PWM rate is shown in Figure 31 and Figure 32. The load disconnect switch improves PWM dynamic range, linearity and color temperature control. To further improve the linearity of PWM dimming, an internal timer delays system shutdown via EN/PWM for 50ms.

FN6626.0

December 17, 2007

FIGURE 31. OPERATION WITH ENL CONTROLLED FET

FIGURE 32. OPERATION WITH NO ENL CONTROLLED FET

#### Bias Current Dimming

Current in the LED load is determined by the value of the feedback resistor and the target feedback regulation voltage as shown in Equation 1:

$$I_{LED} = \frac{V_{FB}}{R_{SENSE}}$$

(EQ. 1)

With MODE tied to VDC, voltage across the feedback resistor is set by V<sub>LEVEL</sub> as shown in Equation 2:

$$V_{FB} = \frac{V_{LEVEL}}{5}$$

(EQ. 2)

The value of V<sub>FB</sub> should be limited to between 50mV and 450mV for linear operation. For minimum light output, VFB may be set below 50mV. With MODE tied to GND, voltage across the feedback resistor is set at ~400mV via an internal reference. In either operating mode, if LED temperature control is enabled, the value of VFB will be reduced when maximum LED temperature is exceeded.

#### Input Overvoltage

For automotive applications, an external high voltage NFET driven by the FAULT pin disconnects the device from the input supply in response to voltage spikes on the input supply. During start-up, an internal charge pump drives the FAULT pin above the input voltage, ensuring the NFET is fully enhanced and powering up the device. In normal operation, the switching node of the boost regulator or the floating supply of the buck regulator is used to pump FAULT above VIN. On detection of an overvoltage, the FAULT pin is discharged to GND. The gate to source voltage of the NDMOS is internally limited to ±15V to prevent voltage stress.

#### **Fault Protection**

The external NFET is also used as a fault protection switch. disconnecting the input supply if a fault occurs for more than 50ms. The system monitors feedback voltage regulation, output overvoltage and input overvoltage. For applications not requiring input voltage or fault protection, connect VBAT and VIN directly together. All faults except input supply overvoltage latch the ISL78100 into an off-state that can be cleared by either power cycling the input supply or the EN/PWM pin. Connecting the TMAX pin to VDC disables the fault latch function (LED over-temperature control is also disabled).

### Output Overvoltage Protection (OVP)

If the FB pin is shorted to ground or an LED fails open circuit. output voltage in BOOST mode can increase to potentially damaging voltages. An optional overvoltage protection circuit can be enabled by connection of the OVP pin to the output voltage. The device will stop switching if the output voltage exceeds OVPH and re-start when the output voltage falls below OVPL. During sustained OVP fault conditions, V<sub>OUT</sub> will saw-tooth between the upper and lower threshold voltages at a frequency determined by the magnitude of current available to discharge the output capacitor and the value of output capacitor used.

The OVP threshold can be set to a lower value by using an external zener diode and resistor, as shown in Figure 33. R<sub>1</sub> should be adjusted to minimize offset in the FB voltage due to FB pin input current. A value of  $100\Omega$  is recommended.

FIGURE 33. EXTERNAL OVP CIRCUIT

#### Over-Temperature Shutdown

An internal sense circuit disables PWM switching if the die temperature exceeds +135°C. Switching is re-enabled when the temperature falls below +100°C.

#### Internal 5V LDO

An internal LDO between VIN and VDC regulates VDC to 5V, to power control and gate drive circuits when V<sub>IN</sub> exceeds 5.1V. In normal operation decouple VDC with at least 3.3µF. In applications where the input supply is less than 5.5V, VDC should be tied directly to VIN.

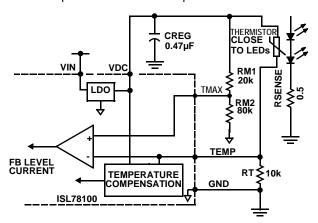

#### **LED Temperature Control**

LED lifetime reduces dramatically with elevated temperature. An over-temperature control circuit utilizing the thermistor voltage at TEMP reduces the LED bias current when VTEMP exceeds the threshold voltage on TMAX. To minimize noise injection, use a potential divider between VDC and GND to set the voltage on TMAX, as shown in Figure 34. The value of TMAX for a specific threshold temperature is determined by the choice of thermistor temperature coefficient. Disable the function by connecting the TMAX pin to VDC and TEMP pin to GND.

FIGURE 34. OVER-TEMPERATURE CIRCUIT

## Component Selection

#### Input Capacitor

Switching regulators require input capacitors to deliver peak charging current and to reduce the impedance of the input supply. This reduces interaction between the regulator and input supply, improving system stability. The high switching frequency of the loop causes almost all ripple current to flow in the input capacitor, which must be rated accordingly.

Considerably more input current ripple is generated in buck mode than boost mode. In buck mode input current is alternately switched between IOUT and zero. The RMS current flow in the input capacitor is given by Equation 3:

$$I_{CAPRMS} = I_{OUT} \bullet \sqrt{(D - D^2)}$$

(EQ. 3)

Where: D = Duty Cycle

The input current is maximum for D = 0.5 and when  $I_{OLIT}$ approaches current limit (2.4A) giving a value of around 1.2A.

A capacitor with low internal series resistance should be chosen to minimize heating effects and improve system efficiency, such as X5R or X7R ceramic capacitors, which offer small size and a lower value of temperature and voltage coefficient compared to other ceramic capacitors.

In boost mode input current flows continuously into the inductor, with an AC ripple component proportional to the rate of inductor charging only and smaller value input capacitors may be used. It is recommended that an input capacitor of at least 10µF be used. Ensure the voltage rating of the input capacitor is suitable to handle the full supply range.

In automotive applications, the input capacitor can be protected from exposure to high voltages present during fault conditions (load dump) by connecting it downstream of the fault protection switch, as shown in Figures 39 and 40.

#### Inductor

Careful selection of inductor value will optimize circuit operation. Inductor type and value influence many key parameters, including ripple current, current limit, efficiency, transient performance and stability. Internal slope compensation has been optimized for inductor values between 4.7µH and 10µH. Ensure the inductor current rating is capable of handling the current limit value in the configuration used (2.4A for buck, 3.5A for boost). If an inductor core is chosen with too low a current rating, saturation in the core will cause the effective inductor value to fall, leading to an increase in peak to average current level, poor efficiency and overheating in the core.

#### Rectifier Diode

A high speed rectifier diode is necessary to prevent excessive voltage overshoot, especially in the boost configuration. Low forward voltage and reverse leakage current will minimize losses, making Schottky diodes the preferred choice. Similarly to the inductor, a diode with a suitable current rating to handle current limit in the configuration must be used.

#### **Output Capacitor**

The output capacitor acts to smooth the output voltage and in the boost configuration supplies load current directly during the conduction phase of the power switch. Ripple voltage consists of two components, the first due to charging and discharging of the capacitor; the second due to IR drop across the ESR of the capacitor by inductor ripple current.

In boost mode:

$$V_{RIPPLE} = \frac{I_O}{C_{OUT}} \times \frac{D}{F_S} + I_{LPK} \times ESR$$

(EQ. 4)

where

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

(EQ. 5)

and

$$I_{LPK} = \frac{I_{O}}{1 - D} + \frac{(V_{OUT} - V_{IN})}{2 \times L} \times \frac{(1 - D)}{f_{S}}$$

(EQ. 6)

In buck mode:

$$V_{\text{RIPPLE}} = \frac{(V_{\text{IN}} - V_{\text{OUT}}) \times D}{2 \times f_{\text{s}} \times L} \times \left(\frac{D}{f_{\text{s}} \times C_{\text{OUT}}} + \text{ESR}\right) \tag{EQ. 7}$$

where:

$$D = \frac{V_{OUT}}{V_{IN}}$$

(EQ. 8)

For a low ESR ceramic capacitor, output ripple is dominated by the charging and discharging of the output capacitor. Care should be taken to ensure the voltage rating of the capacitor exceeds the maximum output voltage.

#### Compensation

The ISL78100 employs a direct summing control loop with current feedback. No error amplifier is used in the system. The arrangement provides fast transient response and makes use of the output capacitor to compensate the loop. The effect of the pole associated with the inductor is minimized by the current feedback. The number of LEDs, their DC bias current and the value of feedback resistor alter loop stability due to their effect on feedback factor, which is heavily influenced by the small signal impedance of the LEDs. Generally, higher numbers of LEDs, lower bias levels and smaller values of feedback resistor will require smaller output capacitors to achieve loop stability. A combination of low ESR electrolytic and ceramic capacitors may be used to reduce implementation costs.

| TARIF 2  | ROOST | MODE   | COMPENSATION.   | 2 7V  | <b>OPERATION</b> |

|----------|-------|--------|-----------------|-------|------------------|

| IADEL 2. | DOOGI | IVIODE | COMIT ENGALION. | Z./ V | OI LIVATION      |

|       |       | VOUT (V)     | 7    | 10.5 | 14   | 17.5 | 21   | 24.5 | 28   |

|-------|-------|--------------|------|------|------|------|------|------|------|

| VFB   | Гоит  | LED's        | 2    | 3    | 4    | 5    | 6    | 7    | 8    |

| 50mV  | 50mA  | Electrolytic | 94µF | 47µF |      |      |      | DMAX | DMAX |

|       |       | Ceramic      | 40µF | 20µF | 40µF | 20μF | 20μF |      |      |

| 100mV | 100mA | Electrolytic | 94µF |      |      |      |      |      |      |

|       |       | Ceramic      | 60µF | 60µF | 40µF | 40µF | 40µF |      |      |

| 200mV | 350mA | Electrolytic | 94µF | 47µF | 47µF | 47μF | ILIM | ILIM | ILIM |

|       |       | Ceramic      | 60µF | 40µF | 40µF | 40μF |      |      |      |

| 200mV | 1A    | Electrolytic | ILIM |

|       |       | Ceramic      |      |      |      |      |      |      |      |

#### TABLE 3. BOOST MODE COMPENSATION 6V OPERATION

|       |       | VOUT (V)     | 7     | 10.5 | 14   | 17.5 | 21   | 24.5 | 28   |

|-------|-------|--------------|-------|------|------|------|------|------|------|

| VFB   | louт  | LED's        | 2     | 3    | 4    | 5    | 6    | 7    | 8    |

| 50mV  | 50mA  | Electrolytic | 94µF  | 47µF |      |      |      |      |      |

|       |       | Ceramic      | 40µF  | 20µF | 40µF | 20μF | 20μF | 20μF | 20µF |

| 100mV | 100mA | Electrolytic | 141µF | 47µF |      |      |      |      |      |

|       |       | Ceramic      | 60µF  | 60µF | 60µF | 40µF | 40μF | 40µF | 40µF |

| 200mV | 350mA | Electrolytic | 141µF | 47µF | 47µF |      |      |      |      |

|       |       | Ceramic      | 60µF  | 60µF | 40µF | 60μF | 40μF | 40µF | 40µF |

| 200mV | 1A    | Electrolytic | 94µF  | 47µF | ILIM | ILIM | ILIM | ILIM | ILIM |

|       |       | Ceramic      | 40µF  | 40µF |      |      |      |      |      |

**TABLE 4. BOOST MODE COMPENSATION 12V OPERATION**

|       |       | VOUT (V)     | 7    | 10.5 | 14   | 17.5 | 21   | 24.5 | 28   |

|-------|-------|--------------|------|------|------|------|------|------|------|

| VFB   | Іоит  | LED's        | 2    | 3    | 4    | 5    | 6    | 7    | 8    |

| 50mV  | 50mA  | Electrolytic |      |      |      |      |      |      |      |

|       |       | Ceramic      | DMIN | DMIN | DMIN | 60µF | 40μF | 40µF | 40µF |

| 100mV | 100mA | Electrolytic |      |      |      | 47µF | 47μF |      |      |

|       |       | Ceramic      | DMIN | DMIN | DMIN | 40µF | 20μF | 40µF | 40µF |

| 200mV | 350mA | Electrolytic |      |      |      | 47µF | 47μF |      |      |

|       |       | Ceramic      | DMIN | DMIN | DMIN | 40µF | 20μF | 40µF | 40µF |

| 200mV | 1A    | Electrolytic |      |      |      | 47µF | 47µF |      |      |

|       |       | Ceramic      | DMIN | DMIN | DMIN | 20µF | 20μF | 40µF | 40µF |

#### **CERAMIC CAPACITORS**

Many ceramic capacitors have strong voltage and temperature coefficients, which reduces effective capacitance as the applied voltage or operating temperature is increased. Pay careful attention when selecting ceramic capacitor type. X5R and X7R families provide much better stability than Y5V, which should generally be avoided unless additional capacitance is added to compensate for the significant changes in value, which occurs overvoltage and temperature.

**TABLE 5. CERAMIC CAPACITOR VARIABILITY**

| CAPACITOR TYPE | TYPICAL VOLTAGE VARIATION | TEMPERATURE VARIATION |

|----------------|---------------------------|-----------------------|

| X7R, 10V       | -30% at 10V               | -15% at +125°C        |

| X5R, 25V       | -50% at 25V               | -9% at +85°C          |

| Y5V, 6.3V      | -90% at 6.3V              | -65% at +85°C         |

#### Layout Considerations

PCB layout is very important for the converter to function properly. The following general guidelines should be followed:

- Separate the Power Ground and Signal Ground; connect them only at one point close to the GND pin.

- Maximize the Power Ground area as much as possible. It is essential to ensure the Power Ground return between C<sub>IN</sub>, C<sub>OUT</sub>, and SWS1,2 as least obstructive as possible.

- Place the input capacitor close to VIN and SWS1, SWS2 pins in boost mode.

- Make the following PC traces as short as possible:

- from SWD1, SWD2 to the inductor in boost mode

- from SWS1,SWS2 to the inductor in buck mode

- from C<sub>OUT</sub> to PGND

- Feedback signals levels are small to improve efficiency. Ensure the reference connection (GND or VIN) between the sense resistor and IC pin doesn't carry switching current.

- · Place several via holes (thermal vias) under the chip to a backside ground plane to improve heat dissipation

- · Maximize the copper area around the thermal vias to spread heat away from the chip.

#### Cost-Sensitive Applications

For cost-sensitive applications, the BOM can be reduced considerably by:

- 1. Removing temperature compensation

- 2. Removing the fault-protection switch

- 3. Removing the load isolation switch

- 4. Switching the FB into internal fixed bias mode (400mV across V<sub>FB</sub>)

In this configuration, light level may be controlled using the EN/PWM input to modulate the output current.

In the absence of the load isolation switch, LED bias current will vary with PWM duty cycle, due to the discharge of the output capacitor by the LED's during the PWM off-time. Therefore, low dimming frequencies can only be used in such an application.

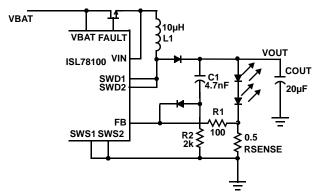

## **Boost Mode Application Diagram**

FIGURE 35. BASIC BOOST APPLICATION CIRCUIT

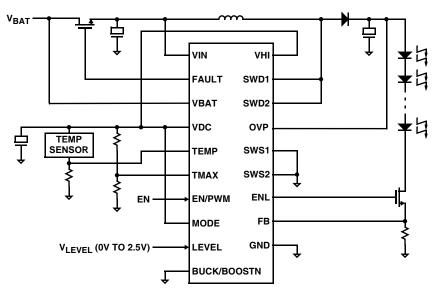

# Boost Mode with Overcurrent Fault and LED Temperature Protections Application Diagram

FIGURE 36. BOOST MODE APPLICATION WITH OVERCURRENT FAULT PROTECTION AND LED TEMPERATURE PROTECTION

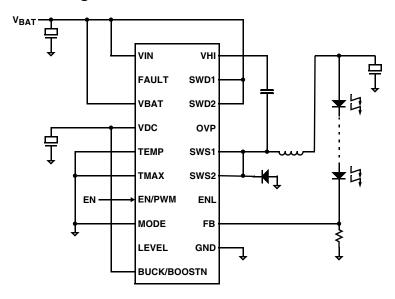

## Typical Buck Application Diagram

FIGURE 37. BASIC BUCK APPLICATION CIRCUIT

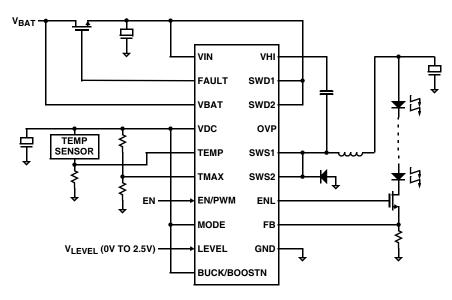

# Buck Mode with Overcurrent Fault and LED Temperature Protections Application Diagram

FIGURE 38. BUCK MODE WITH OVERCURRENT FAULT AND LED TEMPERATURE PROTECTIONS APPLICATION

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

## **Automotive Applications**

The LED load and ISL78100 may be protected against load dumps and other electrical faults in automotive supplies with a minor addition to the standard application schematic:

- A reverse transient automotive-rated protection power Schottky must be added in series with the input supply

- A 500 $\Omega$  current limit resistor must be inserted in series with the VBAT pin

- The fault protection NFET must be specified to handle 100V VDS conditions.

The protection circuit is applicable to buck, boost, and supply-return load applications.

A small reduction in efficiency is caused by the drop in the power Schottky.

Unless alternative transient protection is provided, minimum BOM automotive applications must include the circuit changes noted previously.

## **Automotive Boost Application Diagram**

FIGURE 39. AUTOMOTIVE BOOST MODE APPLICATION DIAGRAM

## Automotive Minimum BOM Boost Application Diagram

FIGURE 40. AUTOMOTIVE MINIMUM BOM BOOST MODE APPLICATION

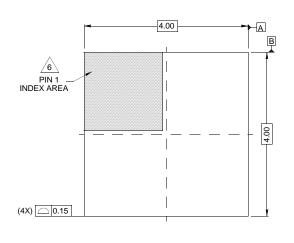

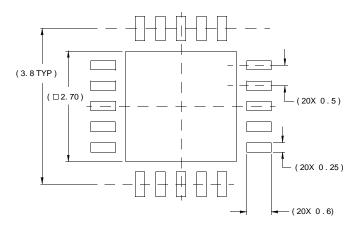

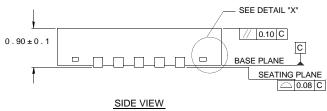

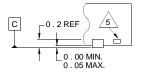

## **Package Outline Drawing**

#### L20.4x4C

# 20 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0, 11/06

TOP VIEW

TYPICAL RECOMMENDED LAND PATTERN

**BOTTOM VIEW**

DETAIL "X"

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.