## 15V/±4A High-Efficiency PWM Power Driver

Check for Samples: DRV595

#### **FEATURES**

- ±4 A Output Current

- Wide Supply Voltage Range: 4.5 V 26 V

- High Efficiency Generates Less Heat

- Multiple Switching Frequencies

- Master/Slave Synchronization

- Up to 1.2 MHz Switching Frequency

- Feedback Power Stage Architecture with High PSRR Reduces PSU Requirements

- Single Power Supply Reduces Component Count

- Integrated Self-Protection Circuits Including Over-Voltage, Under-Voltage, Over-Temperature, and Short Circuit with Error Reporting

- Thermally Enhanced Package

- DAP (32-pin HTSSOP Pad-down)

- –40°C to 85°C Ambient Temperature Range

#### **APPLICATIONS**

- Power Line Communications (PLC) Driver

- Thermoelectric Cooler (TEC) Driver

- Laser Diode Biasing

- Motor Driver

- Servo Amplifier

#### DESCRIPTION

The DRV595 is a high-efficiency, high-current power driver ideal for driving a wide variety of loads in systems powered from 4.5V to 26V. PWM operation and low output stage on-resistance significantly decrease power dissipation in the amplifier.

The DRV595 advanced oscillator/PLL circuit employs multiple switching frequency options; this is achieved together with a Master/Slave option, making it possible to synchronize multiple devices.

The DRV595 is fully protected against faults with short-circuit, thermal, over-voltage, and under-voltage protection. Faults are reported back to the processor to prevent devices from being damaged during overload conditions.

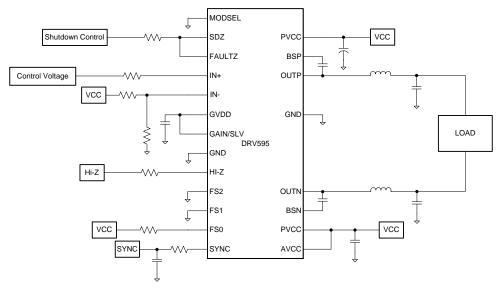

#### SIMPLIFIED APPLICATION CIRCUIT

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

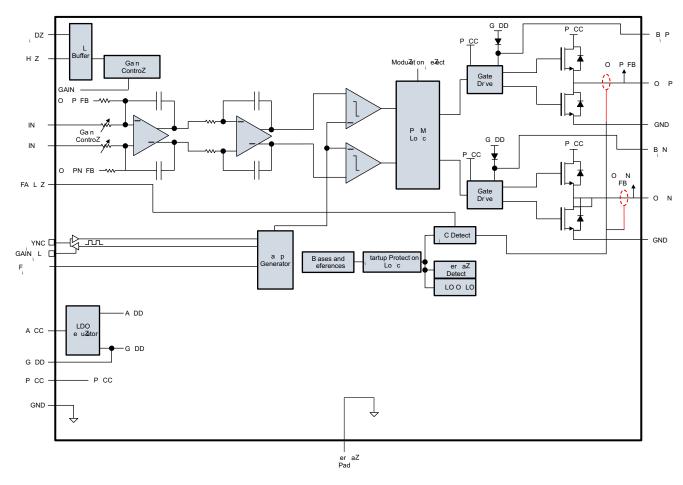

#### **SYSTEM BLOCK DIAGRAM**

### **PINOUT CONFIGURATION**

#### DRV595 32-PIN HTSSOP Package (DAP) (Top View)

Z CC CC A Z B

В

В

.

Z B

, CC CC

Y C A CC

#### Pin Functions

| P         | IN       | TVDE | DESCRIPTION                                                                                                                                                                              |

|-----------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.       | NAME     | TYPE | DESCRIPTION                                                                                                                                                                              |

| 1         | MODSEL   | I    | Mode selection logic input (LOW = BD mode, HIGH = 1SPW mode). TTL logic levels with compliance to AVCC.                                                                                  |

| 2         | SDZ      | I    | Shutdown logic input (LOW = outputs Hi-Z, HIGH = outputs enabled). TTL logic levels with compliance to AVCC.                                                                             |

| 3         | FAULTZ   | DO   | General fault reporting. Open drain. See Table 3 FAULTZ = High, normal operation FAULTZ = Low, fault condition                                                                           |

| 4         | IN+      | 1    | Positive differential input. Biased at 3 V.                                                                                                                                              |

| 5         | IN-      | 1    | Negative differential input. Biased at 3 V.                                                                                                                                              |

| 6, 7      | GVDD     | РО   | Internally generated gate voltage supply. Not to be used as a supply or connected to any component other than a 1 µF X7R ceramic decoupling capacitor and the GAIN/SLV resistor divider. |

| 8         | GAIN/SLV | 1    | Selects Gain and selects between Master and Slave mode depending on pin voltage divider.                                                                                                 |

| 9, 10, 11 | GND      | G    | Ground                                                                                                                                                                                   |

| 12        | Hi-Z     | 1    | Input for fast disable/enable of outputs (HIGH = outputs Hi-Z, LOW = outputs enabled). TTL logic levels with compliance to AVCC.                                                         |

| 13        | FS2      | 1    | Frequency Selection input, used to select oscillator frequencies from 400kHz to 1200kHz.                                                                                                 |

| 14        | FS1      | 1    | Frequency Selection input, used to select oscillator frequencies from 400kHz to 1200kHz.                                                                                                 |

| 15        | FS0      | I    | Frequency Selection input, used to select oscillator frequencies from 400kHz to 1200kHz.                                                                                                 |

| 16        | SYNC     | DIO  | Clock input/output for synchronizing multiple devices. Direction determined by GAIN/SLV terminal.                                                                                        |

| 17        | AVCC     | Р    | Analog Supply, can be connected to PVCC for single power supply operation.                                                                                                               |

| 18, 19    | PVCC     | Р    | Power supply                                                                                                                                                                             |

| 20, 24    | BSN      | BST  | Boot strap for negative output, connect to 220 nF X5R, or better ceramic cap to OUTN                                                                                                     |

| 21        | OUTN     | PO   | Negative output                                                                                                                                                                          |

| 22        | GND      | G    | Ground                                                                                                                                                                                   |

| 23        | OUTN     | PO   | Negative output                                                                                                                                                                          |

| 25        | GND      | G    | Ground                                                                                                                                                                                   |

| 26, 30    | BSP      | BST  | Boot strap for positive output, connect to 220 nF X5R, or better ceramic cap to OUTP                                                                                                     |

Copyright © 2012–2013, Texas Instruments Incorporated

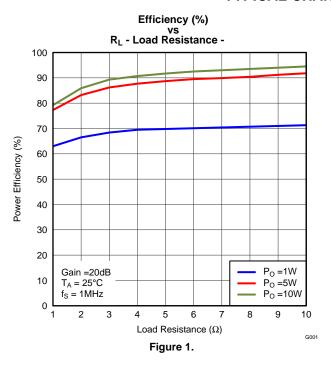

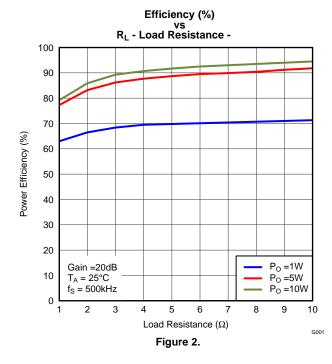

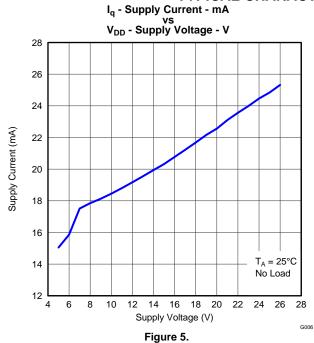

#### **TYPICAL CHARACTERISTICS**

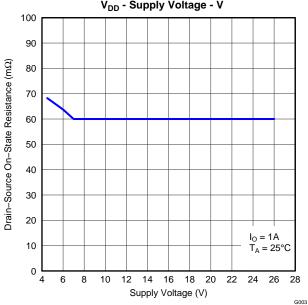

rDS(on) - Drain-Source On-State Resistance m  $_{\rm VS}^{\rm VS}$  V  $_{\rm DD}$  - Supply Voltage - V

Figure 3.

rDS(on) - Drain-Source On-State Resistance m

vs

T<sub>A</sub> - Ambient Temperature - °C

100

90

80

70

60

50

40

30

20

10

Figure 4.

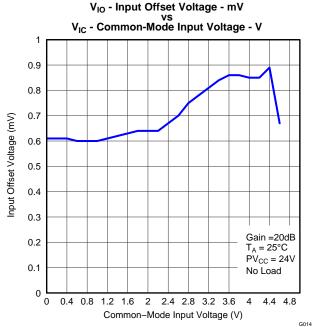

TYPICAL CHARACTERISTICS (continued)

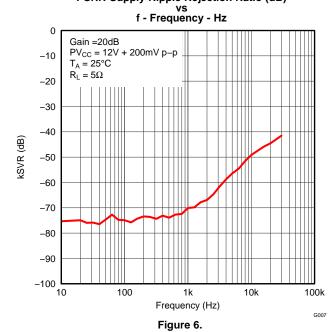

urrent - mA PSRR-Supply Ripple Rejection Ratio (dB)

## PSRR-Supply Ripple Rejection Ratio (dB)

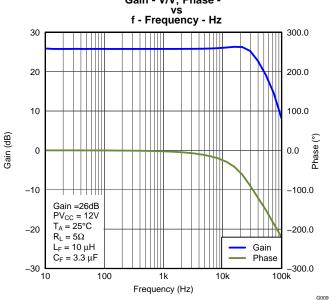

#### Gain - V/V; Phase - °

Figure 7.

Figure 8.

Gain =20dB

$T_A = 25$ °C PV<sub>CC</sub> = 12V

4 4.4 4.8

No Load

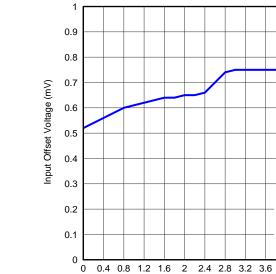

# TYPICAL CHARACTERISTICS (continued) Gain - V/V; Phase - ° V<sub>IO</sub> - Input Offset Voltage - mV

f - Frequency - Hz

Common-Mode Input Voltage (V)

Figure 9. Figure 10.

Figure 11.

Copyright © 2012-2013, Texas Instruments Incorporated

#### **APPLICATION INFORMATION**

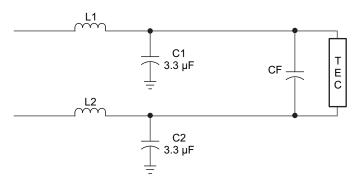

#### **OUTPUT FILTER CONSIDERATIONS**

The DRV595 can be used to drive a TEC element. The typical circuit used for this application is to have two feedback loops – one for constant current, and the second to monitor the temperature, and provide adjustments to keep a constant temperature on the laser diode. An error amplifier is used to combine the two feedback loops, along with a control signal from the system. The output of the error amplifier is then fed into the DRV595.

An output filter needs to be used to prevent excessive ripple from reaching the TEC element. Some TEC elements may be damaged by ripple; design the filter using the TEC specification to reduce the switching waveform enough to prevent TEC damage. This filter also reduces the amount of electrical noise coupled onto the TEC element.

For most applications, a second-order Butterworth low-pass filter with the cut-off frequency set to a few kilohertz should be sufficient. See Figure 12 for example filter designed with Equation 2, Equation 3, and Equation 4.

#### Second-Order Butterworth LPF Transfer Function

$$H(s) = \frac{1}{s^2 + \sqrt{2}s + 1} \tag{1}$$

#### **Using Half-Circuit Analysis**

Figure 12. Second Order Butterworth Low-Pass Filter Configuration

$$L_{x} = \frac{\sqrt{2} \times R_{L}}{2\omega_{o}}$$

$$2 \quad C_{F} \quad \frac{\sqrt{2}}{2 \quad \frac{R_{L}}{2} \quad 0}$$

$$\omega_{0} = 2\pi \times f$$

(2)

$$(3)$$

#### **DEVICE INFORMATION**

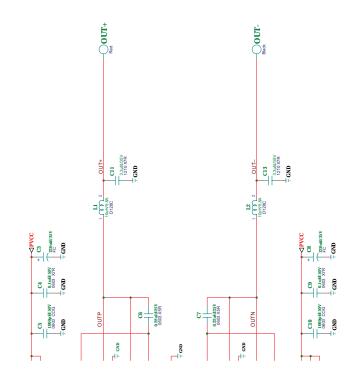

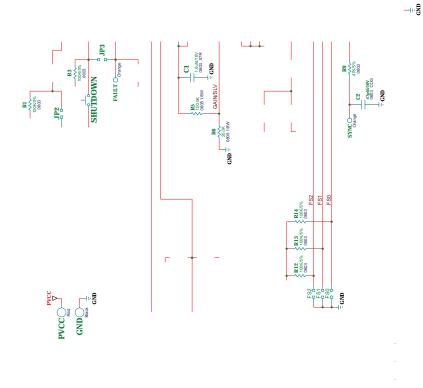

#### **TYPICAL APPLICATION**

Figure 13. Schematic

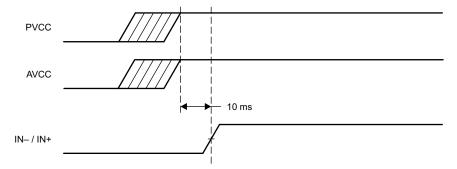

#### START-UP SEQUENCING

To ensure proper operation on power up, wait 10ms after PV<sub>CC</sub> and AV<sub>CC</sub> are stable before using the analog inputs, IN- and IN+. Figure 14 illustrates this sequence.

Figure 14. Start-Up Sequencing (1)

(1) NOTE: The timing relationship between PVCC assertion and AVCC assertion is not critical.

#### **GAIN SETTING AND MASTER / SLAVE**

The gain of the DRV595 is set by the voltage divider connected to the GAIN/SLV control pin. Master or slave mode is also controlled by the same pin. An internal ADC is used to detect the 4 input states. The first four states set the DRV595 in Master mode with gains of 20, 26, 32, 36 dB respectively, while the next four states set the DRV595 in Slave mode with gains of 20, 26, 32, 36 dB respectively. The gain setting is latched during power-up and cannot be changed while the device is powered. Table 1 shows the recommended resistor values for each mode and gain combination:

MACTED / CLAVE

Table 1. GAIN and MASTER/SLAVE

| MASTER / SLAVE<br>MODE | GAIN  | R1 (to GVDD) | R2 (to GND) | INPUT IMPEDANCE |

|------------------------|-------|--------------|-------------|-----------------|

| Master                 | 20 dB | OPEN         | 20 k        | 60 k            |

| Master                 | 26 dB | 100 k        | 20 k        | 30 k            |

| Master                 | 32 dB | 100 k        | 39 k        | 15 k            |

| Master                 | 36 dB | 75 k         | 47 k        | 9 k             |

| Slave                  | 20 dB | 51 k         | 51 k        | 60 k            |

| Slave                  | 26 dB | 47 k         | 75 k        | 30 k            |

| Slave                  | 32 dB | 39 k         | 100 k       | 15 k            |

| Slave                  | 36 dB | 16 k         | 100 k       | 9 k             |

In Master mode, the SYNC terminal is an output, in Slave mode, the SYNC terminal is an input for a clock input. TTL logic levels with compliance to GVDD.

#### **INPUT IMPEDANCE**

The DRV595 input stage is a fully differential input stage and the input impedance changes with the gain setting from 9 k at 36 dB gain to 60 k at 20 dB gain. Table 1 lists the values from min to max gain. The tolerance of the input resistor value is ±20% so the minimum value will be higher than 7.2 k.

**Table 2. Recommended Input AC-Coupling Capacitors**

| GAIN  | INPUT IMPEDANCE |

|-------|-----------------|

| 20 dB | 60 k            |

| 26 dB | 30 k            |

| 32 dB | 15 k            |

| 36 dB | 9 k             |

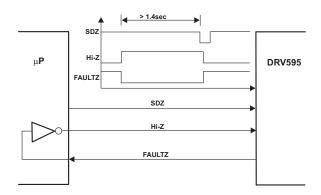

#### START-UP/SHUTDOWN OPERATION

The DRV595 employs a shutdown mode of operation designed to reduce supply current (Icc) to the absolute minimum level during periods of non use for power conservation. The SDZ input terminal should be held high (see specification table for trip point) during normal operation when the amplifier is in use. Pulling SDZ low will put the outputs to Hi-Z and the amplifier to enter a low-current state. It is not recommended to leave SDZ unconnected, because amplifier operation would be unpredictable.

#### **GVDD SUPPLY**

The GVDD Supply is used to power the gates of the output full bridge transistors. It can also be used to supply the GAIN/SLV voltage divider. Decouple GVDD with a X5R ceramic 1 µF capacitor to GND. The GVDD supply is not intended to be used as an external supply. It is recommended to limit the current consumption by using resistor voltage dividers for GAIN/SLV of 100 k or more.

#### **BSP AND BSN CAPACITORS**

#### **DEVICE PROTECTION SYSTEM**

The DRV595 contains a complete set of protection circuits carefully designed to make system design efficient as well as to protect the device against permanent failures due to short circuits, overload,

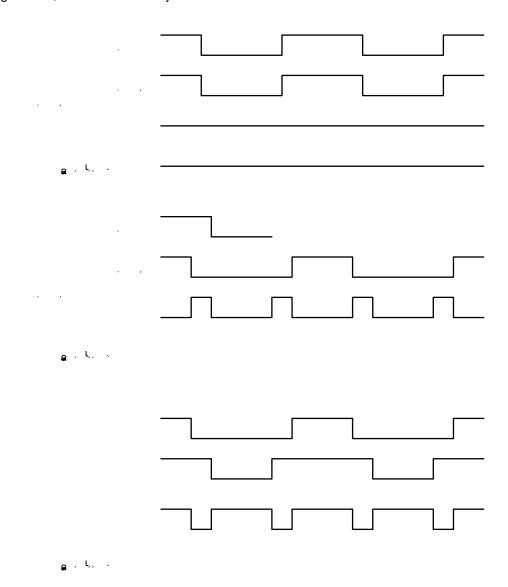

This is a modulation scheme that allows for smaller ripple current through the TEC load. Each output switches from 0 volts to the supply voltage. With no input, OUTP and OUTN are in phase with each other so that there is little or no current in the load. The duty cycle of OUTP is greater than 50% and OUTN is less than 50% for positive output voltages. The duty cycle of OUTP is less than 50% and OUTN is greater than 50% for negative output voltages. The voltage across the load sits at 0V throughout most of the switching period, reducing the switching current, which reduces any I<sup>2</sup>R losses in the load.

Figure 16. BD Mode Modulation

#### POWER DISSIPATION AND MAXIMUM AMBIENT TEMPERATURE

Though the DRV595 is much more efficient than traditional linear solutions, the power drop across the onresistance of the output transistors does generate some heat in the package, which may be calculated as shown in Equation 5:

$$P_{DISS} = \left(I_{OUT}\right)^{2} \times r_{DS(on), \text{ total For example, at the maximum output current of 3 A through a total on-resistance}$$

of 60 m (at T<sub>J</sub> = 25°C), the power dissipated in the package is 1.1 W. (5)

Calculate the maximum ambient temperature using Equation 6:

$$T_{A} = T_{J} - (\theta_{JA} \times P_{DISS})$$

(6)

## PRINTED-CIRCUIT BOARD (PCB LAYOUT)

It is necessary to take care when planning the layout of the printed circuit board. The following suggestions will help to meet EMC requirements.

- Decoupling capacitors The high-frequency decoupling capacitors should be placed as close to the PVCC and AVCC terminals as possible. Large (100 F or greater) bulk power supply decoupling capacitors should be placed near the DRV595 on the PVCC supplies. Local, high-frequency bypass capacitors should be placed as close to the PVCC pins as possible. These caps can be connected to the IC GND pad directly for an excellent ground connection. Consider adding a small, good quality low ESR ceramic capacitor between 220 pF and 1 nF and a larger mid-frequency cap of value between 100 nF and 1 μF also of good quality to the PVCC connections at each end of the chip.

- Grounding The PVCC decoupling capacitors should connect to GND. All ground should be connected at the IC GND, which should be used as a central ground connection or star ground for the DRV595.

For an example layout, see the DRV595 Evaluation Module (DRV595EVM) User Manual. Both the EVM user's manual and the thermal pad application report are available on the TI Web site at http://www.ti.com.

#### **REVISION HISTORY**

#### Changes from Original (December 2012) to Revision A

Page

Copyright © 2012–2013, Texas Instruments Incorporated

## **PACKAGE OPTION ADDENDUM**

11-Apr-2013

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        |                  | (3)                 |              | (4)               |         |

| DRV595DAP        | ACTIVE | HTSSOP       | DAP     | 32   | 46      | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | DRV595            | Samples |

| DRV595DAPR       | ACTIVE | HTSSOP       | DAP     | 32   | 2000    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | DRV595            | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS)5 (Tesmis)r()\$ "42235-(Fleed:9:nf 9351-62e¢") r442275-(Testis)r()\$ "42235-(Fleed:9:nf 6381617) (Q) 2 e" (2807)26(d3) 23.(726 e") 2606001/07232(1) 8492275-7(26sidio2327-BIF 1/6"3-E736h(BiFt)ve-Bet")/BIFT/934608001/07099999 re b-Free""Pb-Free"

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

## PACKAGE MATERIALS INFORMATION

www.ti.com 14-Mar-2013

### TAPE AND REEL INFORMATION

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV595DAPR | HTSSOP          | DAP                | 32 | 2000 | 330.0                    | 24.4                     | 8.6        | 11.5       | 1.6        | 12.0       | 24.0      | Q1               |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 14-Mar-2013

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV595DAPR | HTSSOP       | DAP             | 32   | 2000 | 367.0       | 367.0      | 45.0        |

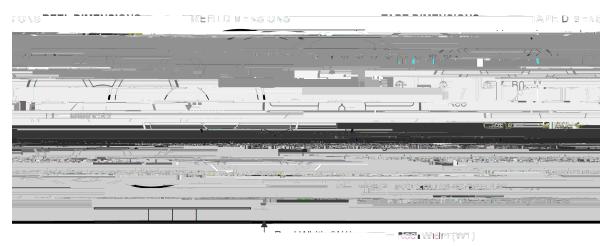

### THERMAL INFORMATION

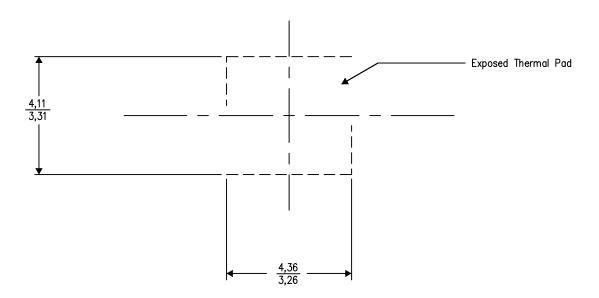

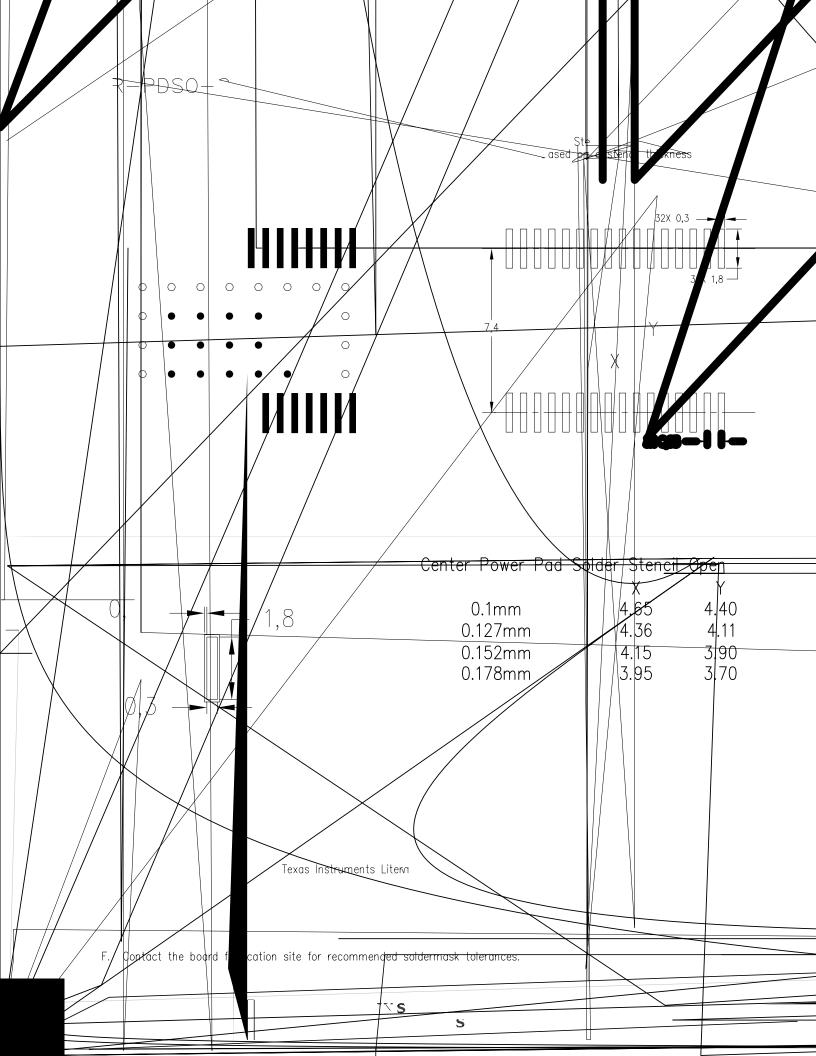

transfer from the integrated circuit (IC).

cdvantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both (

The exposed thermal pad dimensions for this package are shown in the following illustration.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>