n, \

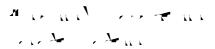

- ➤ Multifunction charge/discharge counter

- ➤ Resolves signals less than 12.5µV

- ➤ Internal offset calibration improves accuracy

- ➤ 1024 bits of NVRAM configured as 128 x 8

- ➤ Internal temperature sensor for self-discharge estimation

- ➤ Single-wire serial interface

- ➤ Dual operating modes:

- Operating: <80μA

- Sleep: <10μA

- ➤ REG output for low-cost microregulation

- ➤ Internal timebase eliminates external components

- ➤ 8-pin TSSOP or SOIC allows battery pack integration

... - ... - ...

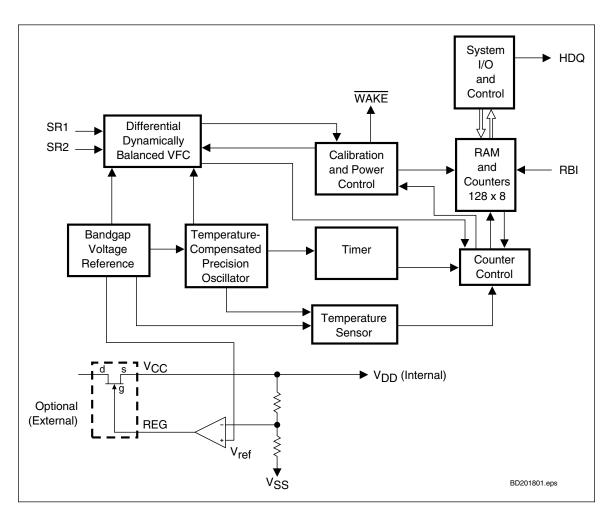

The bq2018 is a low-cost charge/discharge counter peripheral packaged in an 8-pin TSSOP or SOIC. It works with an intelligent host controller, providing state-of-charge information for rechargeable batteries.

The bq2018 measures the voltage drop across a low-value series sense resistor between the negative terminal of the battery and the battery pack ground contact. By using the accumulated counts in the charge, discharge, and self-discharge registers, an intelligent host controller can determine battery state-of-charge information. To improve accuracy, an offset count register is available. The system host controller is responsible for the register maintenance by resetting the charge in/out and self-discharge registers as needed.

The bq2018 also features 128 bytes of NVRAM registers. The upper 13 bytes of NVRAM contain the capacity monitoring and status information. The RBI input operates from an external power storage source such as a capacitor or a series cell in the battery pack, providing register nonvolatility for periods when the battery is shorted to ground or when the battery charge state is not sufficient to operate the bq2018. During this mode, the register backup current is less than 100nA.

Packaged in an 8-pin TSSOP or SOIC

### - 11 / 17 T 11 11

REG

REG is the output of the operational transconductance amplifier (OTA) that drives an external pass n-channel JFET to provide an optional regulated supply. The supply is

regulated at 3.7V nominal.

Regulator output

### V<sub>CC</sub> Supply voltage input

When regulated by the REG output,  $V_{\rm CC}$  is 3.7V ±200mV. When the REG output is not used, the valid operating range is 2.8V to 5.5V.

### V<sub>SS</sub> Ground

#### SR1- Current sense inputs SR2

The bq2018 interprets charge and discharge activity by monitoring and integrating the voltage drop  $(V_{SR})$  across pins SR1 and SR2. The SR1 input connects to the sense resistor and the negative terminal of the battery. The SR2 input connects to the sense resistor and the negative terminal of the pack.  $V_{SR1}$  and the negative terminal of the pack.  $V_{SR2}$  indicates discharge, and  $V_{SR1} > V_{SR2}$  indicates charge. The effective voltage drop,  $V_{SR0}$ , as seen by the bq2018, is  $V_{SR} + V_{OS}$ . Valid input range is  $\pm$  200mV.

### HDQ Data input/output

This bi-directional input/output communicates the register information to the host system. HDQ is open drain and requires a pullup/down resistor in the battery pack to disable/enable sleep mode if the pack is removed from the system.

### RBI Register backup input

This input maintains the internal register states during periods when  $V_{\rm CC}$  is below the minimum operating voltage.

### WAKE Wake-up output

When asserted, this output is used to indicate that the charge or discharge activity is above a programmed minimal level.

A host can use the bq2018 internal counters and timers to measure battery state-of-charge, estimate self-discharge, and calculate the average charge and dis-

# 1., 1. , 4 , 1,.

| - 11     | -1/1/1 |                       |        | , 1, , 1, |

|----------|--------|-----------------------|--------|-----------|

| HDQ High | yes    | $ V_{SRO}  > V_{WOE}$ | Low    | Normal    |

| HDQ High | yes    | $ V_{SRO}  < V_{WOE}$ | High Z | Normal    |

| HDQ Low  | no     | $ V_{SRO}  < V_{WOE}$ | High Z | Sleep     |

Note:  $V_{SRO}$  is the voltage difference between SR1 and SR2 plus the offset voltage  $V_{OS}$ .

$$n_{i_1} = 2.$$

\* A

The RBI input pin is used with a storage capacitor or external supply to provide back-up potential to the internal RAM when  $V_{CC}$  drops below 2.4V. The maximum discharge current is 100nA in this mode. The bq2018 outputs  $V_{CC}$  on RBI when the supply is above 2.4V, so a diode is required to isolate an external supply.

Table 2 shows the main counters and registers of the bq2018. The bq2018 accumulates charge and discharge counts into two main count registers, the Discharge Count Register (DCR) and the Charge Count Register (CCR). The bq2018 produces charge and discharge

counts by sensing the voltage difference across a low-value resistor between the negative terminal of the battery pack and the negative terminal of the battery. The DCR or CCR counts depending on the signal between SR1 and SR2.

During discharge, the DCR and the Discharge Time Counter (DTC) are active. If  $V_{\rm SR1}$  is less than  $V_{\rm SR2}$ , indicating a discharge, the DCR counts at a rate equivalent to 12.5µV every hour, and the DTC counts at a rate of 1 count/0.8789 seconds (4096 counts per 1 hour). For example, a -100mV signal produces 8000 DCR counts and 4096 DTC counts each hour. The amount of charge removed from the battery can easily be calculated.

1., 2., 201

| ш,           | 7 111                         | n <sub>tt</sub>                                              | 1      |

|--------------|-------------------------------|--------------------------------------------------------------|--------|

| DCR          | Discharge count register      | $V_{SR1} < V_{SR2}$ (Max. =-200mV) 12.5 $\mu$ Vh increments  | 16-bit |

| CCR          | Charge count register         | $V_{SR1} > V_{SR2}$ (Max. = +200mV) 12.5 $\mu$ Vh increments | 16-bit |

| SCR          | Self-discharge count register | $1 \operatorname{count/hour} @ 25^{\circ}\mathrm{C}$         | 16-bit |

| DTC          | Discharge time counter        | 1 count/0.8789s default<br>1 count/225s if STD is set        | 16-bit |

| СТС          | Charge time counter           | 1 count/0.8789s default<br>1 count/225s if STC is set        | 16-bit |

| MODE/<br>WOE | MODE/<br>Wake output enable   | _                                                            | 8-bit  |

During charge, the CCR and the Charge Time Counter (CTC) are active. If  $V_{\rm SR1}$  is greater than  $V_{\rm SR2}$ , indicating a charge, the CCR counts at a rate equivalent to  $12.5\mu V$  every hour, and the CTC counts at a rate of 1 count/0.8789 seconds. For example, a +100mV signal produces 8000 CCR counts and 4096 CTC counts each hour. The amount of charge added to the battery can easily be calculated.

The DTC and the CTC are 16-bit registers, and roll over beyond ffffh. If a rollover occurs, the corresponding bit in the MODE/WOE register is set, and the counter will subsequently increment at 1/256 of the normal rate (16 counts/hr)

Whenever the signal between SR1 and SR2 is above the Wakeup Output Enable (WOE) threshold and the HDQ pin is high, the bq2018 is in its full operating state. In this state, the DCR, CCR, DTC, CTC, and SCR are fully operational, and the  $\overline{\text{WAKE}}$  output is low. During this mode, the internal RAM registers of the bq2018 may be accessed over the HDQ pin, as described in the section "Communicating With the 2018."

If the signal between SR1 and SR2 is below the WOE threshold (refer to the  $\overline{WAKE}$  section for details) and HDQ remains low for greater than 10 seconds, the bq2018 enters a sleep mode where all register counting is suspended. The bq2018 remains in this mode until HDQ returns high.

For self-discharge calculation, the self-discharge count register (SCR) counts at a rate equivalent to 1 count every hour at a nominal  $25^{\circ}$ C and doubles approximately every 10°C up to 60°C. The SCR count rate is halved every 10 °C below  $25^{\circ}$ C down to 0°C. The value in SCR is

useful in determining an estimation of the battery selfdischarge based on capacity and storage temperature conditions.

| ٧., 3. | _ | 1 | -, <b></b> - | 1 | k | 1 | , |

|--------|---|---|--------------|---|---|---|---|

|--------|---|---|--------------|---|---|---|---|

| ~ 31(, ) | , ( ,) |

|----------|--------|

| 0h       | n/a    |

| 1h       | 3.840  |

| 2h       | 1.920  |

| 3h       | 1.280  |

| 4h       | 0.960  |

| 5h       | 0.768  |

| 6h       | 0.640  |

| 7h*      | 0.549  |

| · · · · · · · · · · · · · · · · · · · |           |             |  |  |  |  |  |  |  |

|---------------------------------------|-----------|-------------|--|--|--|--|--|--|--|

| ,1                                    | ( , ) , د | , 1 - , 11, |  |  |  |  |  |  |  |

| <0°                                   | 0h        | × 1/8       |  |  |  |  |  |  |  |

| 0-10°                                 | 1h        | × 1/4       |  |  |  |  |  |  |  |

| 10–20°                                | 2h        | × 1/2       |  |  |  |  |  |  |  |

| 20–30°                                | 3h        | 1 count/hr. |  |  |  |  |  |  |  |

| 30–40°                                | 4h        | $\times 2$  |  |  |  |  |  |  |  |

| 40–50°                                | 5h        | $\times 4$  |  |  |  |  |  |  |  |

| 50–60°                                | 6h        | × 8         |  |  |  |  |  |  |  |

| >60°                                  | 7h        | × 16        |  |  |  |  |  |  |  |

### , 1 , 2 --

The bq2018 has an internal temperature sensor which is used to set the value in the temperature register (TMP/CLR) and set the self-discharge count rate value. The register reports the temperature in 8 steps of  $10^{\circ}\mathrm{C}$  from <0°C to >60°C as Table 4 specifies. The bq2018 temperature sensor has typical accuracy of  $\pm 2^{\circ}\mathrm{C}$  at  $25^{\circ}\mathrm{C}$ . See the TMP/CLR register description for more details.

The host system is responsible for register maintenance. To facilitate this maintenance, the bq2018 has a Clear Register (TMP/CLR) designed to reset the specific counter or register pair to zero. The host system clears a register by writing the corresponding register bit to 1. When the bq2018 completes the reset, the corresponding bit in the TMP/CLR register is automatically reset to 0, which saves the host an extra write/read cycle. Clearing the DTC register clears the STD bit and sets the DTC count rate to the default value of 1 count per 0.8789s. Clearing

the CTC register clears the STC bit and sets the CTC count rate to the default value of 1 count per 0.8789s.

The system can enable bq2018  $V_{OS}$  calibration by setting the calibration bit in the MODE/WOE register (Bit 6) to 1. The bq2018 then enters calibration mode when the HDQ line is low for greater than 10 seconds and when the signal between SR1 and SR2 is below  $V_{WOE}$ . Caution: Take care to ensure that no low-level external signal is present between SR1 and SR2 because this affects the calibration value that the bq2018 calculates.

If HDQ remains low for one hour and  $|V_{\rm SR}| < V_{\rm WOE}$  for the entire time, the measured  $V_{\rm OS}$  is latched into the OFR register, and the calibration bit is reset to zero, indicating to the system that the calibration cycle is complete. Once calibration is complete, the bq2018 enters a

$$n_{ij} = 4$$

.  $n_{ij} = 1$   $n_$

<sup>\*</sup> Default value after POR.

| <b>1., 5., 201</b> | -11 | 1,1 | 1,1 | • 1 |  | ' · 1 | · · | -,- |  |

|--------------------|-----|-----|-----|-----|--|-------|-----|-----|--|

|--------------------|-----|-----|-----|-----|--|-------|-----|-----|--|

|              |                                               |       | 1,11/          |        |       |       |       | - м. 1 |       |       |        |

|--------------|-----------------------------------------------|-------|----------------|--------|-------|-------|-------|--------|-------|-------|--------|

| , 1 .        | 'Ri',                                         | (``)  | 7, 11          | 7( ^ ) | 6     | 5     | 4     | 3      | 2     | 1     | 0( ^ ) |

| CMDR         | Command register                              | -     | Write          | W/R    | AD6   | AD5   | AD4   | AD3    | AD2   | AD1   | AD0    |

| DCRH         | Discharge count<br>register high<br>byte      | 7f    | Read           | DCRH7  | DCRH6 | DCRH5 | DCRH4 | DCRH3  | DCRH2 | DCRH1 | DCRH0  |

| DCRL         | Discharge<br>count register<br>low byte       | 7e    | Read           | DCRL7  | DCRL6 | DCRL5 | DCRL4 | DCRL3  | DCRL2 | DCRL1 | DCRL0  |

| CCRH         | Charge count<br>register<br>high byte         | 7d    | Read           | CCRH7  | CCRH6 | CCRH5 | CCRH4 | CCRH3  | CCRH2 | CCRH1 | CCRH0  |

| CCRL         | Charge count<br>register<br>low byte          | 7c    | Read           | CCRL7  | CCRL6 | CCRL5 | CCRL4 | CCRL3  | CCRL2 | CCRL1 | CCRL0  |

| SCRH         | Self-discharge<br>count register<br>high byte | 7b    | Read           | SCRH7  | SCRH6 | SCRH5 | SCRH4 | SCRH3  | SCRH2 | SCRH1 | SCRH0  |

| SCRL         | Self-discharge<br>count register<br>low byte  | 7a    | Read           | SCRL7  | SCRL6 | SCRL5 | SCRL4 | SCRL3  | SCRL2 | SCRL1 | SCRL0  |

| DTCH         | Discharge<br>time count<br>high byte          | 79    | Read           | DTCH7  | DTCH6 | DTCH5 | DTCH4 | DTCH3  | DTCH2 | DTCH1 | DTCH0  |

| DTCL         | Discharge<br>time count<br>low byte           | 78    | Read           | DTCL7  | DTCL6 | DTCL5 | DTCL4 | DTCL3  | DTCL2 | DTCL1 | DTCL0  |

| СТСН         | Charge<br>time count<br>high byte             | 77    | Read           | СТСН7  | СТСН6 | СТСН5 | CTCH4 | стснз  | CTCH2 | CTCH1 | СТСН0  |

| CTCL         | Charge<br>time count<br>low byte              | 76    | Read           | CTCL7  | CTCL6 | CTCL5 | CTCL4 | CTCL3  | CTCL2 | CTCL1 | CTCL0  |

| MODE/<br>WOE | MODE/ wake-<br>up output<br>enable            | 75    | Read/<br>write | OVRDQ  | CAL   | STC   | STD   | WOE3   | WOE2  | WOE1  | 0      |

| TMP/CLR      | Tempera-<br>ture/Clear<br>register            | 74    | Read/<br>write | TMP2   | TMP1  | TMP0  | CTC   | DTC    | SCR   | CCR   | DCR    |

| OFR          | Offset<br>register                            | 73    | Read/<br>write | OFR7   | OFR6  | OFR5  | OFR4  | OFR3   | OFR2  | OFR1  | OFR0   |

| RAM          | User<br>memory                                | 72-00 | Read/<br>write | -      | -     | -     | -     | -      | -     | -     | -      |

Notes:

- 1. MODE/WOE register bit 0 is set to zero at startup and should not be written to 1 for proper bq2018 operation.

- $2. \quad OFR \ value \ is \ in \ two's \ complement.$

low-power mode until HDQ goes high, indicating an external system is ready to access the bq2018. If HDQ transitions high prior to completion of the  $V_{\rm OS}$  calculation or if  $|V_{\rm SR}| > V_{\rm WOE}$ , then the calibration cycle is reset. The bq2018 then postpones the calibration cycle until the conditions are met. The calibration bit does not reset to zero until a valid calibration cycle is completed. The requirement for HDQ to remain low for the calibration cycle can be disabled by setting the OVRDQ bit to 1. In this case, calibration continues as long as  $|V_{\rm SR}| < V_{\rm WOE}$ . The OVRDQ bit is reset to zero at the end of a valid calibration cycle.

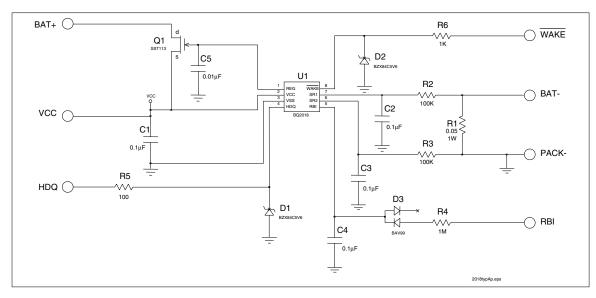

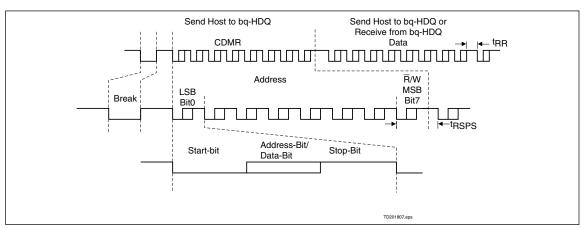

The bq2018 includes a simple single-pin (referenced to  $V_{\rm SS})$  serial data interface. A host processor uses the interface to access various bq2018 registers. Battery activity may be easily monitored by adding a single contact to the battery pack. Note: The HDQ pin requires an external pull-up or pull-down resistor.

The interface uses a command-based protocol, where the host processor sends a command byte to the bq2018. The command directs the bq2018 either to store the next eight bits of data received to a register specified by the command byte or to output the eight bits of data from a register specified by the command byte.

The communication protocol is asynchronous return-toone. Command and data bytes consist of a stream of eight bits that have a maximum transmission rate of 5K bits/sec. The least-significant bit of a command or data byte is transmitted first. The protocol is simple enough that it can be implemented by most host processors using either polled or interrupt processing. Data input from the bq2018 may be sampled using the pulse-width capture timers available on some microcontrollers. A UART may also be used to communicate through the HDQ pin.

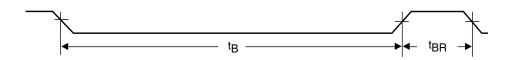

If a communication time-out occurs, e.g., the host waits longer than  $t_{\rm CYCB}$  for the bq2018 to respond or if this is the first access command, then a BREAK should be sent by the host. The host may then resend the command. The bq2018 detects a BREAK when the HDQ pin is driven to a logic-low state for a time,  $t_{\rm B}$  or greater. The HDQ pin then returns to its normal ready-high logic state for a time,  $t_{\rm BR}$ . The bq2018 is then ready to receive a command from the host processor.

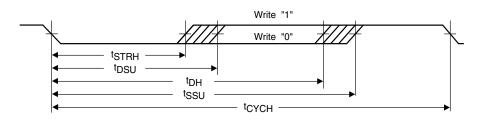

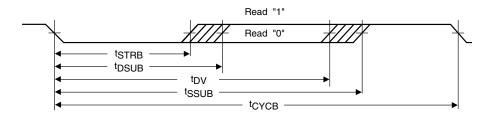

The return-to-one data bit frame consists of three distinct sections. The first section is used to start the transmission by either the host or the bq2018 taking the HDQ pin to a logic-low state for a period,  $t_{\rm STRH,B}$ . The next section is the actual data transmission, where the data should be valid by a period,  $t_{\rm DSU,B}$ , after the negative edge used to start communication. The data should be held for a period,  $t_{\rm DV}/t_{\rm DH}$ , to allow the host or bq2018 to sample the data bit

The final section is used to stop the transmission by returning the HDQ pin to a logic-high state by at least a period,  $t_{\rm SSU,B}$ , after the negative edge used to start communication. The final logic-high state should be held until a period,  $t_{\rm CYCH,B}$ , to allow time to ensure that the bit transmission ceased properly. The serial communication timing specification and illustration sections give the timings for data and break communication.

Communication with the bq2018 always occurs with the least-significant bit being transmitted first. Figure 4 shows an example of a communication sequence to read the bq2018 OFR register.

The bq2018 command and status registers are listed in Table 5 and described below.

The write-only command register is accessed when the bq2018 has received eight contiguous valid command bits. The command register contains two fields:

- W/R

- Command address

The  $W\overline{R}$  bit of the command register is used to select whether the received command is for a read or a write function. The  $W\overline{R}$  values are

|     |   |   | - | , |   |   |   |

|-----|---|---|---|---|---|---|---|

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| W/R | - | - | - | - | - | - | - |

Where  $W/\overline{R}$  is

of the discharge, and are incremented whenever  $V_{\rm SR1} < V_{\rm SR2}$ . These registers continue to count beyond ffffh, so proper register maintenance should be done by the host system. The TMP/CLR register is used to force the reset of both the DCRH and DCRL to zero.

The CCRH high-byte register (address = 7dh) and the CCRL low-byte register (address = 7ch) contain the count of the charge, and are incremented whenever  $V_{\rm SR1} > V_{\rm SR2}.$  These registers continue to count beyond ffffh, so proper register maintenance should be done by the host system. The TMP/CLR register is used to force the reset of both the CCRH and CCRL to zero.

The SCRH high-byte register (address = 7bh) and the SCRL low-byte register (address = 7ah) contain the self-discharge count. This register is continually updated whenever the bq2018 is in its normal operating mode. The counts in these registers are incremented based on time and temperature. The SCR counts at a rate of 1 count per hour at 20–30°C and doubles every 10°C to greater than 60°C (16 counts/hour). The count will half every 10°C below 20–30°C to less than 0°C (1 count/8 hours). These registers continue to count beyond ffffh, so proper register maintenance should be done by the host system. The TMP/CLR register is used to force the reset of both the SCRH and SCRL to zero.

The DTCH high-byte register (address = 79h) and the DTCL low-byte register (address = 78h) are used to determine the length of time the  $V_{\rm SR1} < V_{\rm SR2}$  indicating a discharge. The counts in these registers are incremented at a rate of 4096 counts per hour. If the DTCH/DTCL register continues to count beyond ffffh, the STD bit is set in the MODE/WOE register indicating a rollover. Once set, DTCH and DTCL increment at a rate of 16 counts per hour. Note: If a second rollover occurs, STD is cleared. Access to the bq2018 should be timed to clear DTCH/DTCL more often than every 170 days. The TMP/CLR register is used to force the reset of both the DTCH and DTCL to zero.

The CTCH high-byte register (address = 77h) and the CTCL low-byte register (address = 76h) are used to determine the length of time the  $V_{\rm SR1} > V_{\rm SR2}$  indicating a charge. The counts in these registers are incremented at a rate of 4096 counts per hour. If the CTCH/CTCL registers continue to count beyond ffffh, the STC bit is set in the MODE/WOE register indicating a rollover. Once set,

DTCH and DTCL increment at a rate of 16 counts per hour. Note: If a second rollover occurs, STC is cleared. Access to the bq2018 should be timed to clear CTCH/CTCL more often than every 170 days. The TMP/CLR register is used to force the reset of both the CTCH and CTCL to zero.

The Mode/WOE register (address = 75h) contains the calibration, wakeup enable information, and the STC and STD bits as described below.

The Override DQ(OVRDQ) bit (bit 7) is used to override the requirement for HDQ to be low prior to initiating  $V_{OS}$  calibration. This bit is normally set to zero. If OVRDQ is written to one, the bq2018 begins offset calibration when  $|V_{SR}|\!<\!V_{WOE}\!$  where HDQ = Don't care.

The OVRDQ location is

|       |   |   | _ 1 |   |   |   |   |

|-------|---|---|-----|---|---|---|---|

| 7     | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

| OVRDQ | - | - | -   | - | - | - | - |

Where OVRDQ is

- 0 HDQ = 0 and  $|V_{SR}| < V_{WOE}$  for  $V_{OS}$  calibration to begin

- 1 HDQ = Don't care and  $|V_{SR}| < V_{WOE}$  for  $V_{OS}$  calibration to begin

Note: The OVRDQ bit should only be used in conjunction with a calibration cycle. Normal operation of the bq2018 cannot be guaranteed when this bit is set. After a valid calibration cycle, bit 7 is reset to zero.

The calibration (CAL) bit 6 is used to enable the bq2018 offset calibration test. Setting this bit to 1 enables a  $V_{\rm OS}$  calibration whenever HDQ is low (default), and  $|V_{\rm SRO}| < V_{\rm WOE}$ . This bit is cleared to 0 by the bq2018 whenever a valid  $V_{\rm OS}$  calibration is completed, and the OFR register is updated with the new calculated offset. The bit remains 1 if the offset calibration was not completed.

The CAL location is

|   |     |   | _ 1 | _ ^ | . • |   |   |

|---|-----|---|-----|-----|-----|---|---|

| 7 | 6   | 5 | 4   | 3   | 2   | 1 | 0 |

| - | CAL | - | -   | -   | -   | - | - |

Where CAL is

- 0 Valid offset calibration

- 1 Offset calibration pending

The slow time charge (STC) and slow time discharge (STD) flags indicate if the CTC or DTC registers have rolled over beyond ffffh. STC set to 1 indicates a CTC rollover; STD set to 1 indicates a DTC rollover.

The STC and STD locations are

|   |   |     | ,-  | 1 , |   |   |   |

|---|---|-----|-----|-----|---|---|---|

| 7 | 6 | 5   | 4   | 3   | 2 | 1 | 0 |

| - | - | STC | STD | -   | - | - | - |

Where STC/STD is

- 0 No rollover

- 1 Rollover occurred in the corresponding CTC/DTC register.

The Wake Up Output Enable (WOE) bits (bits 3–1) are used to set the Wake-Up Enable signal level. Whenever  $\mid V_{SRO} \mid < V_{WOE},$  the WAKE output is in High Z. If  $\mid V_{SRO} \mid$  is greater than  $V_{WOE},$  WAKE transitions low. On bq2018 initialization (power-on reset) these bits are set to 1. Setting all of these bits to zero is not valid. Refer to Table 3 for the various WOE values.

The WOE 3-1 locations are

| -1 - 1. |   |   |   |      |      |      |   |  |

|---------|---|---|---|------|------|------|---|--|

| 7       | 6 | 5 | 4 | 3    | 2    | 1    | 0 |  |

| -       | - | - | - | WOE3 | WOE2 | WOE1 | - |  |

Where WOE3–1 is determined by dividing 3.84mV by the value in WOE.

Bit 0 is reserved and must remain 0.

| 1, 1, 1, 1, 1, | 14,,,,, |

|----------------|---------|

|----------------|---------|

The TMP/CLR register (address = 74h) is used to give the present temperature step between <  $0^{\circ}$ C to >  $60^{\circ}$ C and clear the various count registers. The values of the TMP0–TMP2 (bits 5–7) denote the current temperature step sense by the bq2018 as outlined in Table 4. The bq2018 temperature sense is trimmed to  $\pm$  2°C typical ( $\pm$  4°C maximum).

The TMP2-0 locations are

|    | - 1- 1 · |      |      |   |   |   |   |   |  |  |  |

|----|----------|------|------|---|---|---|---|---|--|--|--|

| 7  |          | 6    | 5    | 4 | 3 | 2 | 1 | 0 |  |  |  |

| TM | P2       | TMP1 | TMP0 | - | - | - | - | - |  |  |  |

Where TMP2-0 is the temperature step sensed by this bq2018.

The Clear bits (Bits 0–4) are used to reset the various bq2018 counters and STC and STD bits to zero. Writing the bits to 1 resets the corresponding register to 0. The clear bit resets to 0 indicating a successful register reset. Each clear bit is independent, so it is possible to clear the DCRH/DCRL registers without affecting the values in any other bq2018 register. The high-byte and low-byte registers are both cleared when the corresponding bit is written to 1 per the figure below.

$M_{ij} = 5.$

### The Clear bit locations are

| , /_ r · |   |               |     |     |     |     |     |  |  |  |

|----------|---|---------------|-----|-----|-----|-----|-----|--|--|--|

| 7        | 6 | 6 5 4 3 2 1 0 |     |     |     |     |     |  |  |  |

| -        | - | -             | CTC | DTC | SCR | CCR | DCR |  |  |  |

### Where:

CTC bit (bit 4) resets both the CTCH and CTCL registers and the STC bit to 0.

The DTC bit (bit 3) resets both the DTCH  $\,$  and DTCL registers and the STD bit to 0.

The SCR bit (bit 2) resets both the SCRH  $\,$  and SCRL registers to 0.

The CCR bit (bit 1) resets both the CCRH  $\,$  and CCRL registers to 0.

The DCR bit (bit 0) resets both the DCRH  $\,$  and DCRL registers to 0.

The OFR register (address = 73h) is used to store the calculated  $V_{\rm OS}$  of the bq2018. The OFR value can be used to cancel the voltage offset between  $V_{\rm SR1}$  and  $V_{\rm SR2}$ . The up/down offset counter is centered at zero. The actual offset is an 8-bit two's complement value located in OFR.

#### The OFR locations are

|               | Mt A |      |      |      |      |      |      |  |  |  |  |

|---------------|------|------|------|------|------|------|------|--|--|--|--|

| 7 6 5 4 3 2 1 |      |      |      |      |      |      | 0    |  |  |  |  |

| OFR7          | OFR6 | OFR5 | OFR4 | OFR3 | OFR2 | OFR1 | OFR0 |  |  |  |  |

Where OFR7 is

- 1 Discharge

- 0 Charge

#

| , 1.,                              | سرر الدان                 | . [ ]             | 1   1                 | k  | 1,,,                                                                                                       |

|------------------------------------|---------------------------|-------------------|-----------------------|----|------------------------------------------------------------------------------------------------------------|

| $V_{CC}$                           | Relative to $V_{\rm SS}$  | -0.3              | +6.0                  | V  |                                                                                                            |

| HDQ                                | Relative to $ m V_{SS}$   | -0.3              | +6.0                  | V  |                                                                                                            |

| All other pins                     |                           | $ m V_{SS}$ -0.3V | $V_{\rm CC}$ +3.0 $V$ | V  |                                                                                                            |

| $I_{ m REG}$                       | REG to $ m V_{SS}$        |                   | 1.0                   | mA |                                                                                                            |

| V <sub>SR1</sub> /V <sub>SR2</sub> | Relative to ${ m V_{SS}}$ | -0.3              | +6.0                  | V  | A $100 \mathrm{k}\Omega$ series resistor is recommended to protect SR1 / SR2 in case of a shorted battery. |

| $T_{\mathrm{OPR}}$                 | Operating temperature     | - 20              | +70                   | °C |                                                                                                            |

Note: Permanent device damage may occur if **Absolute Maximum Ratings** are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

## · , ~ | h , , ~ | h , ~ e . ( \_ · . , )

| ر د اد ر | سرر الدار                              | ١, ، | 1 1 / |    | 1,                                                                          |

|----------|----------------------------------------|------|-------|----|-----------------------------------------------------------------------------|

| $V_{OS}$ | Offset voltage                         |      | ±500  | μV | Voltage offset between SR1 and SR2                                          |

| OSC      | Timer accuracy                         | 1.5  | ±3.0  | %  | $V_{CC} = 3.5 - 3.9 V (T_A = 0-70^{\circ}C)$                                |

| INR      | Integrated non-<br>repeatability error | 0.5  | 1.0   | %  | Measured repeatability given similar operating conditions                   |

| INL      | Integrated non-linearity               | 1.0  | 2.0   | %  | Add 0.05% per °C above or below 25°C and 0.5% per volt above or below 3.7V. |

# ,1,114, + -11 (e) " ( 1 ", , , , e) " ( ( , , , )

| ٠. ا . ر          | . L. L                             | 1 1,, | ١, , ١ | \   |    | 1                       |

|-------------------|------------------------------------|-------|--------|-----|----|-------------------------|

| $t_{CYCH}$        | Cycle time, host to bq2018 (write) | 190   | -      | -   | μs |                         |

| $t_{CYCB}$        | Cycle time, bq2018 to host (read)  | 190   | 205    | 250 | μs |                         |

| ${ m t_{STRH}}$   | Start hold, host to bq2018 (write) | 5     | -      | -   | ns |                         |

| ${ m t_{STRB}}$   | Start hold, bq2018 to host (read)  | 32    | -      | -   | μs |                         |

| $t_{DSU,B}$       | Data setup                         | -     | -      | 50  | μs |                         |

| $t_{ m DH}$       | Data hold                          | 90    | -      | -   | μs |                         |

| $t_{\mathrm{DV}}$ | Data valid                         | -     | -      | 80  | μs |                         |

| $t_{SSUB}$        | Stop setup (bq2018 to host)        | -     | -      | 95  | μs |                         |

| $t_{ m SSU}$      | Stop setup (host to bq2018)        | -     | -      | 145 | μs |                         |

| $t_{\mathrm{B}}$  | Break                              | 190   | -      | -   | μs |                         |

| $t_{ m BR}$       | Break recovery                     | 40    | -      | -   | μs |                         |

| $t_{RSPS}$        | Response time, bq2018 to host      | 190   | -      | 320 | μs |                         |

| $t_{ m RR}$       | Read recovery                      | 40    | -      | -   | μs | Host read to next cycle |

#

# ., **201** . . .

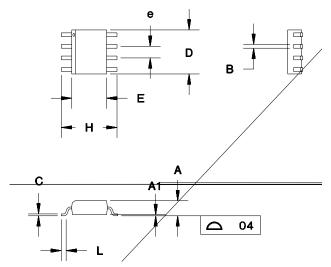

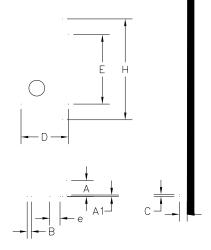

## 8-Pin SOIC Narrow ~ SN Package Suffix

|           | Millim | neters | Inches |       |  |  |  |

|-----------|--------|--------|--------|-------|--|--|--|

| Dimension | Min.   | Max.   | Min.   | Max.  |  |  |  |

| A         | 1.52   | 1.78   | 0.060  | 0.070 |  |  |  |

| A1        | 0.10   | 0.25   | 0.004  | 0.010 |  |  |  |

| В         | 0.33   | 0.51   | 0.013  | 0.020 |  |  |  |

| C         | 0.18   | 0.25   | 0.007  | 0.010 |  |  |  |

| D         | 4.70   | 5.08   | 0.185  | 0.200 |  |  |  |

| E         | 3.81   | 4.06   | 0.150  | 0.160 |  |  |  |

| e         | 1.14   | 1.40   | 0.045  | 0.055 |  |  |  |

| Н         | 5.72   | 6.22   | 0.225  | 0.245 |  |  |  |

| L         | 0.38   | 0.89   | 0.015  | 0.035 |  |  |  |

## **Data Sheet Revision History**

| Change No. | Page No. | Description | Nature of Change                              |

|------------|----------|-------------|-----------------------------------------------|

| 1          | All      |             |                                               |

| 2          | 12       |             | Clarification of absolute maximum pin ratings |

Note: Change 1 = Jan. 1999 B changes to Final from Dec. 1998 Preliminary data sheet.

Change 2 = June 1999 C changes from Jan. 1999 B.

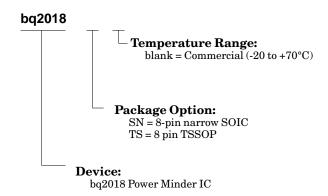

## **Ordering Information**

## Notes

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

### PACKAGE OPTION ADDENDUM

ww.ti.com 11-Apr-2013

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|------------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

| BQ2018SN-E1      | ACTIVE     | SOIC         | D                  | 8    | 75             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM  | -20 to 70    | 2018              | Samples |

| BQ2018SN-E1TR    | ACTIVE     | SOIC         | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM  | -20 to 70    | 2018              | Samples |

| BQ2018SN-E1TRG4  | ACTIVE     | SOIC         | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM  | -20 to 70    | 2018              | Samples |

| BQ2018TS-E1      | ACTIVE     | TSSOP        | PW                 | 8    | 150            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -20 to 70    | BQ218             | Samples |

| BQ2018TS-E1TR    | ACTIVE     | TSSOP        | PW                 | 8    | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -20 to 70    | BQ218             | Samples |

| BQ2018TS-E1TRG4  | ACTIVE     | TSSOP        | PW                 | 8    | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -20 to 70    | BQ218             | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

### PACKAGE OPTION ADDENDUM

www.ti.com 11-Apr-2013

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Jan-2013

### TAPE AND REEL INFORMATION

\*All dimensions are nominal

| I | Device        | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|---------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

|   | BQ2018SN-E1TR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| ı | BQ2018TS-E1TR | TSSOP           | PW                 | 8 | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Jan-2013

### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ2018SN-E1TR | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| BQ2018TS-E1TR | TSSOP        | PW              | 8    | 2000 | 367.0       | 367.0      | 35.0        |

Texas Instruments Incorporated and it changes to its semiconductor products issue. Buyers should obtain the latest r complete. All semiconductor products (a supplied at the time of order acknowledge)

TI warrants performance of its component and conditions of sale of semiconductor put to support this warranty. Except where mal performed.

TI assumes no liability for applications assist applications using TI components. To minimize adequate design and operating safeguards.

TI does not warrant or represent that any licens other intellectual property right relating to any copublished by TI regarding third-party products or endorsement thereof. Use of such information mathird party, or a license from TI under the patents of

Reproduction of significant portions of TI information