## LCD Segment Driver series

# For 72/80/96 Segment type LCD

# **LCD Segment Driver**

# BU9735K, BU9796FS, BU9716BKV, BU9718KV

## Outline

This is LCD segment driver for 72-96 segment type display. There is a lineup which is suitable for multi function display and is integrated display RAM and power supply circuit for LCD driving with 4 common output type: BU9735K and BU9796FS. And 3 common output type: BU9716BKV and BU9718KV.

| 0 | 72Segment (18SEG×4COM) Driver | BU9735K            | ••••••P.1 |  |

|---|-------------------------------|--------------------|-----------|--|

| 0 | 80Segment (20SEG×4COM) Driver | BU9796FS           | •••••P.9  |  |

| 0 | 96Segment (32SEG×3COM) Driver | BU9716BKV/BU9718KV | •••••P.19 |  |

96Segment (32SEG×3COM) Driver BU9716BKV/BU9718KV

# **BU9735K**

72Segment (18SEG×4COM) Driver

- Feature

- 1) 4wire serial interface (SCK, SD,  $\overline{C/D}$ ,  $\overline{CS}$ )

- 2) Integrated RAM for display data (DDRAM) : 18 × 4bit (Max 72 Segment)

- 3) LCD driving port: 4 Common output, 18 Segment output

- 4) Display duty: 1/4 duty

- 5) Integrated Oscillator circuit (external resister type)

- 6) Integrated Power supply circuit for LCD driving (1/3 bias)

- 7) Low power/ Ultra low power consumption design: +2.5~5.5V

- Uses

DVC, Car audio, Telephone

## Absolute Maximum Ratings (Ta=25degree, VSS=0V) (BU9735K)

| / tooolato maximani r tatingo | (      | ogioo, voo ov/ (E | 0010010 |                                                      |

|-------------------------------|--------|-------------------|---------|------------------------------------------------------|

| Parameter                     | Symbol | Limits            | Unit    | Remarks                                              |

| Power Supply Voltage1         | VDD    | -0.3 ~ +7.0       | V       | Power supply                                         |

| Power Supply Voltage2         | VLCD   | -0.3 ~ +7.0       | V       | LCD drive voltage                                    |

| Allowable loss                | Pd     | 400               | mW      | When use more than Ta=25°C, subtract 4mW per degree. |

| Operational temperature range | Topr   | -40 ~ +85         | Degree  |                                                      |

| Storage temperature range     | Tstg   | -55 ~ +125        | Degree  |                                                      |

| Input voltage range           | VIN    | -0.3 to VDD*0.3   | V       |                                                      |

| Output voltage range          | VOUT   | -0.3 to VDD+0.3   | V       |                                                      |

|                               |        |                   |         |                                                      |

\*This product is not designed against radioactive ray.

#### • Recommend operating conditions (Ta=25degree, VSS=0V) (BU9735K)

| Parameter             | Symbol | MIN | TYP | MAX | Unit | Remarks     |

|-----------------------|--------|-----|-----|-----|------|-------------|

| Power Supply Voltage1 | VDD    | 2.2 | -   | 5.5 | V    |             |

| Power Supply Voltage2 | VLCD   | 2.5 | -   | 5.5 | V    | VLCD≧VC≧VSS |

| Oscillator frequency  | fOSC   | -   | 36  | -   | KHz  | Rf=470kΩ    |

### \*This document is not delivery specifications.

## • Electrical Characteristics (BU9735K)

DC Characteristics (VDD=2.5~5.5V, VSS=0V, Ta=25degree, unless otherwise specified)

| Deremeter                | Symb |         | Limit |         | Linit | Condition                 | Terminel                                    |

|--------------------------|------|---------|-------|---------|-------|---------------------------|---------------------------------------------|

| Parameter                | ol   | Min.    | Тур.  | Max.    | Unit  | Condition                 | Terminal                                    |

| "H" level input voltage  | VIH1 | 0.8×VDD | -     | VDD     | v     |                           | SC1, SD, SCK,                               |

| "L" level input voltage  | VIL1 | 0       | -     | 0.2×VDD | v     |                           | C/D, CS                                     |

| LCD Driver on resistance | RON  | -       | -     | 30      | KΩ    | ∆VON =0.1V                | SEG1~18, COM1~4                             |

| "H" level input current  | IIH  | -2      | -     | -       | uA    | VIN=VDD                   | OSC1, SD, SCK,                              |

| "L" level input current  | IIL  | -       | -     | 2       | uA    | VIN=0                     | C/D, CS,                                    |

| Input capacitance        | CI   | -       | 5     | -       | pF    |                           | SD, SCK, $\overline{C/D}$ , $\overline{CS}$ |

|                          |      | -       | 0.05  | 1       | uA    | <sup>*2</sup> Display OFF |                                             |

| Power consumption        | IDD  | -       | 30    | 70      | uA    | <sup>*2</sup> Display ON  | VDD                                         |

|                          |      | -       | 80    | 200     | uA    | <sup>*3</sup> MPU Access  |                                             |

\*1: LCD Driver on resistance is not included internal power supply impedance.

\*2: VLCD=VDD, Rf=470Kohm, except of OSC1 terminals are connected to VDD or VSS.

\*3: VLCD=VDD, Rf=470Kohm, fSCK=200KHz

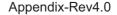

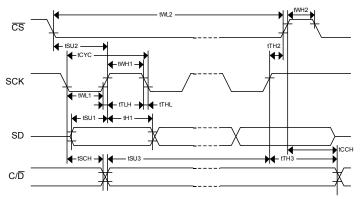

AC Characteristics (VDD=2.5~5.5V, VSS=0V, Ta=25degree, unless otherwise specified)

| Parameter                                             | Symbol |      | Limit |      | Unit | Condition                                         |

|-------------------------------------------------------|--------|------|-------|------|------|---------------------------------------------------|

| Parameter                                             | Symbol | Min. | Тур.  | Max. | Unit | Condition                                         |

| SCK rise time                                         | tTLH   | -    | -     | 100  | ns   |                                                   |

| SCK fall time                                         | tTHL   | -    | -     | 100  | ns   |                                                   |

| SCK cycle time                                        | tCYC   | 800  | -     | -    | ns   |                                                   |

| Wait time for command                                 | tWAIT  | 800  | -     | -    | ns   |                                                   |

| SCK pulse width H"                                    | tWH1   | 300  | -     | -    | ns   |                                                   |

| SCK pulse width "L"                                   | tWL1   | 300  | -     | -    | ns   |                                                   |

| SD setup time                                         | tSU1   | 100  | -     | -    | ns   |                                                   |

| SD hole time                                          | tH1    | 100  | -     | -    | ns   |                                                   |

| CS pulse width "H"                                    | tWH2   | 300  | -     | -    | ns   |                                                   |

| CS pulse width "L"                                    | tWL2   | 6400 | -     | -    | ns   |                                                   |

| CS setup time                                         | tSU2   | 100  | -     | -    | ns   |                                                   |

| CS hold time                                          | tH2    | 100  | -     | -    | ns   |                                                   |

| C / D setup time                                      | tSU3   | 100  | -     | -    | ns   |                                                   |

| C / D hold time                                       | tH3    | 100  | -     | -    | ns   | Based on SCK 8 <sup>th</sup> clock rising         |

| $\overline{C/D}$ - $\overline{CS}$ time <sup>*4</sup> | tCCH   | 100  | -     | -    | ns   | Based on CS rising                                |

| C/D - SCK time*4                                      | tSCH   | 100  | -     | -    | ns   | Based o SCK 8 <sup>th</sup> clock falling         |

| Display start delay time                              | tON    | 140  | -     | -    | ns   | SCK 8 <sup>th</sup> clock rising to display start |

\*4: should satisfy either one condition

Fig. BU9735K-1 Interface timing

Fig. BU9735K-2 Command cycle

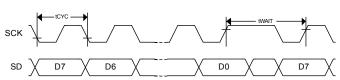

## • Block Diagram (BU9735K)

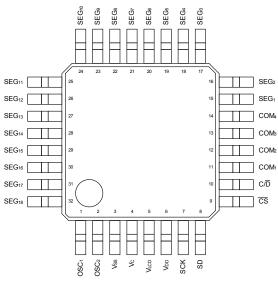

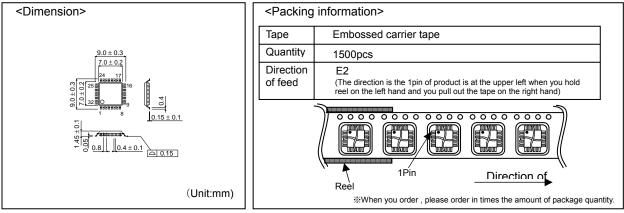

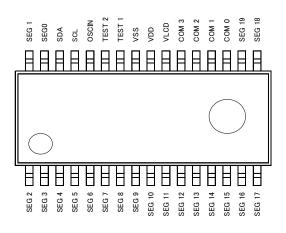

## •Pin Arrangement (BU9735K)

Fig. BU9735K-3 Block diagram

Fig. BU9735KV-4 Pin arrangement

| • | Terminal | description | (BU9735K) |

|---|----------|-------------|-----------|

|---|----------|-------------|-----------|

| Terminal     | No.    | Туре   | Function                                                                                                                  |  |  |  |  |

|--------------|--------|--------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OSC1<br>OSC2 | 1<br>2 | I<br>O | Int clock use mode, connect resister between OSC1 and OSC2.<br>Ext clock use mode, input clock from OSC1, OSC2 keep OPEN. |  |  |  |  |

| VSS          | 3      |        | VSS terminal                                                                                                              |  |  |  |  |

| VC<br>VLCD   | 4<br>5 |        | Power supply for LCD driving<br>Please keep VLCD≧VC≧VSS condition                                                         |  |  |  |  |

| VDD          | 6      |        | VDD terminal                                                                                                              |  |  |  |  |

| SCK          | 7      | Ι      | Serial clock input                                                                                                        |  |  |  |  |

| SD           | 8      | Ι      | Serial data input                                                                                                         |  |  |  |  |

| CS           | 9      | Ι      | Chip select input "L": active,                                                                                            |  |  |  |  |

| C/D          | 10     | I      | Command data judgment input<br>"L": display data, "H": command                                                            |  |  |  |  |

| COM1~4       | 11~14  | 0      | LCD COMMON output                                                                                                         |  |  |  |  |

| SEG1~18      | 15~32  | 0      | LCD SEGMENT output                                                                                                        |  |  |  |  |

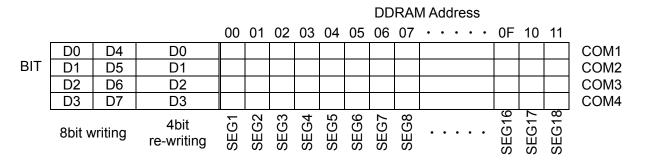

Block Description (BU9735K)

## ○ ADDRESS COUNTER

An address counter shows the address of DDRAM. Address data are transferred to the address counter automatically when an address set is written in the command/data register.

After data are written in DDRAM, +1 or +2 is done automatically with an address counter. The choice of +1 or +2 is done automatically by the next condition.

DDRAM 8bit writing (in the 8 clock of SCK, C/D= "L")  $\rightarrow$  +2

DDRAM 4bit rewriting (in the 8 clock of SCK, C/D= "H")  $\rightarrow$  +1

And, when it is counted to 11H, an address becomes 00H with an address counter by the next count up.

## ○ DISPLAY DATA RAM (DDRAM)

A display data RAM (DDRAM) is used to store display data. That capacity is 18 address × 4 bits. DDRAM and the relations of the display position are as the following.

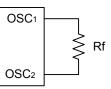

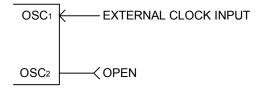

## ○ TIMING GENERATER

A built-in oscillator circuit does oscillated by connecting Rf between OSC1, OSC2, and an indication timing signal is caused. And, it is possible that it is made to work by the external clock input, too.

(It is possible that Oscillating Frequency is changed with Rf. )

Fig. BU9735K-5 Rf Oscillator Circuit

Fig. BU9735K-6 External Clock Input

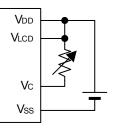

## ○ LCD DRIVE POWER SUPPLY

LCD drive power supply occurs by BU9735K.

LCD voltage is given by VC, and it causes V1=(2/3) VC, V2=(1/3) VC.

Fig. BU9735K-7 Internal Power Supply use

## • DETAILS OF COMMANDS (BU9735K)

There is the following thing in the command (The 8×n clock of SCK is C/D= "H".) of BU9735K.

|               | S SET      | -                |                     |          |           |         |        |          |                                                               |

|---------------|------------|------------------|---------------------|----------|-----------|---------|--------|----------|---------------------------------------------------------------|

|               | MSB        |                  |                     |          |           |         |        | LSB      |                                                               |

|               | 0          | 0                | 0                   | А        | Α         | А       | Α      | Α        |                                                               |

|               |            |                  |                     |          | -         | -       | •      |          | et on the address counter.<br>) completes input.              |

|               |            |                  |                     |          |           |         |        |          |                                                               |

|               | MSB        | 0                | 4                   | *        | *         | *       | *      | LSB<br>* |                                                               |

|               | 0          | 0                | 1                   | Ŷ        | Â         | Ŷ       | Ŷ      | Ŷ        |                                                               |

| There a       | re no r    | elatio           | ns with             | the c    | ontent    | s of th | e disr | lav dat  | * : Don't Care<br>ta RAM (DDRAM).                             |

|               |            |                  |                     |          |           |         |        | •        | DDRAM don't change.                                           |

| o - · - · · · |            |                  |                     |          |           |         |        |          | -                                                             |

|               | OFF<br>MSB |                  |                     |          |           |         |        |          | LSB                                                           |

|               | 0          | 1                | 0                   | *        | *         | *       | *      | *        | LOD                                                           |

|               | 0          | I                | 0                   |          |           |         |        |          | * : Don't Care                                                |

| And all       | display    | / is tur         | ned of              | ff. A bu | uilt-in p | ower    | supply | circuit  | ta RAM (DDRAM).<br>t is turned off.<br>of DDRAM don't change. |

|               |            |                  |                     |          |           |         |        |          |                                                               |

|               | MSB        |                  |                     |          |           |         |        |          | LSB                                                           |

|               | 0          | 1                | 1                   | *        | *         | *       | *      | *        |                                                               |

| Display       | is star    | ted in           | accor               | dance    | with th   | ne con  | tents  | of DDR   | * : Don't Care                                                |

| Diopidy       | io otai    |                  | accon               | auroo    | with the  |         |        |          |                                                               |

|               |            | F THE            | DISP                | LAY D    | DATA R    | RAM (E  | DRA    | M)       |                                                               |

|               | MSB        |                  |                     |          |           |         |        |          | LSB                                                           |

|               | 1          | 0                | 0                   | *        | D         | D       | D      | D        |                                                               |

|               | g addre    | ess is           | addre               | ss ord   | ered b    | y the a | addres | ss set o | * : Don't Care<br>command.<br>s + 1 automatically.            |

|               |            |                  |                     |          |           |         |        |          |                                                               |

|               | MSB        |                  |                     |          |           |         |        |          | LSB                                                           |

|               | 1          | 1                | 0                   | *        | *         | *       | *      | *        |                                                               |

|               |            |                  |                     |          |           |         |        |          | * : Don't Care                                                |

|               |            | itialize<br>Disp | ed in th<br>lay off | ne follo | owing o   | conditi |        |          | ands after POWER-on, and carry it out.<br>mmand.              |

|               | •          | Add              | ess c               | Junter   | resett    | ing     |        |          |                                                               |

Oscillation stop

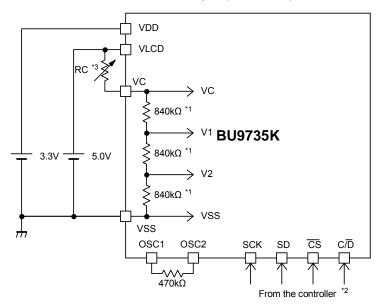

## Recommendation circuit example (BU9735K)

- \*1 The value  $(840k\Omega)$  of the built-in resistance value in the figure is reference value. Value varies according to terms of manufacture and so on.

- \*2 The maximum value of the signal of the control isn't to use higher value than VDD. (Refer to the regulation of the input voltage in the specifications.)

- \*3 It can use as a resistance for the contrast adjustment when variable resistance is given to the VLCD-VC space. In this case, the resistance of the outside and resistance with built-in BU9735K become connections like a left figure. The value of RC is to decide the value, which met a system referring to the circuit of the left figure.

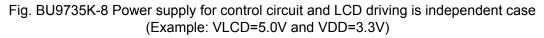

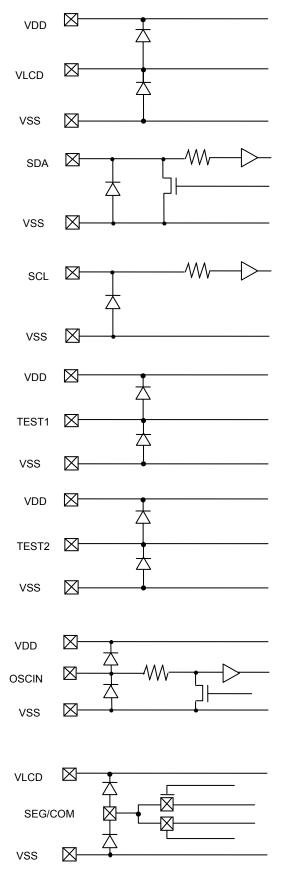

Fig.BU9735K-9 I/O circuit

### • Cautions on use

#### (1) Absolute Maximum Ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down devices, thus making impossible to identify breaking mode such as a short circuit or an open circuit. If any special mode exceeding the absolute maximum ratings is assumed, consideration should be given to take physical safety measures including the use of fuses, etc.

#### (2) Operating conditions

These conditions represent a range within which characteristics can be provided approximately as expected. The electrical characteristics are guaranteed under the conditions of each parameter.

#### (3) Reverse connection of power supply connector

The reverse connection of power supply connector can break down ICs. Take protective measures against the breakdown due to the reverse connection, such as mounting an external diode between the power supply and the IC's power supply terminal.

#### (4) Power supply line

Design PCB pattern to provide low impedance for the wiring between the power supply and the GND lines. In this regard, or the digital block power supply and the analog block power supply, even though these power supplies has the same level of potential, separate the power supply pattern for the digital block from that for the analog block, thus suppressing the diffraction of digital noises to the analog block power supply resulting from impedance common to the wiring patterns. For the GND line, give consideration to design the patterns in a similar manner. Furthermore, for all power supply terminals to ICs, mount a capacitor between the power supply and the GND terminal. At the same time, in order to use an electrolytic capacitor, thoroughly check to be sure the characteristics of the capacitor to be used present no problem including the occurrence of capacity dropout at a low temperature, thus determining the constant.

#### (5) GND voltage

Make setting of the potential of the GND terminal so that it will be maintained at the minimum in any operating state. Furthermore, check to be sure no terminals are at a potential lower than the GND voltage including an actual electric transient.

#### (6) Short circuit between terminals and erroneous mounting

In order to mount ICs on a set PCB, pay thorough attention to the direction and offset of the ICs. Erroneous mounting can break down the ICs. Furthermore, if a short circuit occurs due to foreign matters entering between terminals or between the terminal and the power supply or the GND terminal, the ICs can break down.

#### (7) Operation in strong electromagnetic field

Be noted that using ICs in the strong electromagnetic field can malfunction them.

#### (8) Inspection with set PCB

On the inspection with the set PCB, if a capacitor is connected to a low-impedance IC terminal, the IC can suffer stress. Therefore, be sure to discharge from the set PCB by each process. Furthermore, in order to mount or dismount the set PCB to/from the jig for the inspection process, be sure to turn OFF the power supply and then mount the set PCB to the jig. After the completion of the inspection, be sure to turn OFF the power supply and then dismount it from the jig. In addition, for protection against static electricity, establish a ground for the assembly process and pay thorough attention to the transportation and the storage of the set PCB.

#### (9) Input terminals

In terms of the construction of IC, parasitic elements are inevitably formed in relation to potential. The operation of the parasitic element can cause interference with circuit operation, thus resulting in a malfunction and then breakdown of the input terminal. Therefore, pay thorough attention not to handle the input terminals, such as to apply to the input terminals a voltage lower than the GND respectively, so that any parasitic element will operate. Furthermore, do not apply a voltage to the input terminals when no power supply voltage is applied to the IC. In addition, even if the power supply voltage is applied, apply to the input terminals a voltage lower than the power supply voltage or within the guaranteed value of electrical characteristics.

#### (10) Ground wiring pattern

If small-signal GND and large-current GND are provided, It will be recommended to separate the large-current GND pattern from the small-signal GND pattern and establish a single ground at the reference point of the set PCB so that resistance to the wiring pattern and voltage fluctuations due to a large current will cause no fluctuations in voltages of the small-signal GND. Pay attention not to cause fluctuations in the GND wiring pattern of external parts as well.

#### (11) External capacitor

In order to use a ceramic capacitor as the external capacitor, determine the constant with consideration given to a degradation in the nominal capacitance due to DC bias and changes in the capacitance due to temperature, etc.

#### (12) No Connecting input terminals

In terms of extremely high impedance of CMOS gate, to open the input terminals causes unstable state. And unstable state brings the inside gate voltage of p-channel or n-channel transistor into active. As a result, battery current may increase. And unstable state can also causes unexpected operation of IC. So unless otherwise specified, input terminals not being used should be connected to the power supply or GND line.

#### (13) Rush current

When power is first supplied to the CMOS IC, it is possible that the internal logic may be unstable and rush current may flow instantaneously. Therefore, give special condition to power coupling capacitance, power wiring, width of GND wiring, and routing of connections.

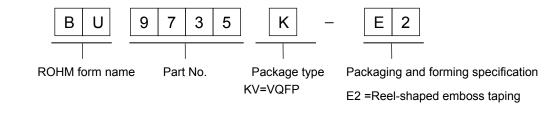

• Order form name selection

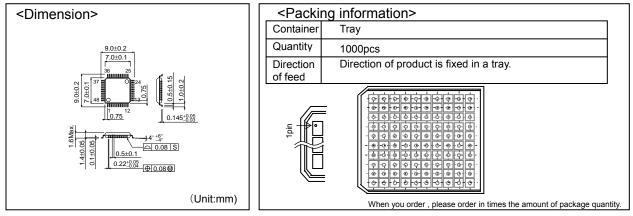

QFP32

## **BU9796FS**

## 80Segment (20SEG×4COM) Driver

- Feature (BU9796FS)

- 1) 2wire serial interface

- 2) Integrated RAM for display data (DDRAM) : 20 × 4bit (Max 80 Segment)

- 3) LCD driving port: 4 Common output, 20 Segment output

- 4) Display Duty: 1/4 duty

- 5) Integrated Oscillation circuit

- 6) Integrated Buffer AMP for LCD driving power supply circuit

- 7) Support 1/2bias, 1/3bias select

- 8) No external components

- 9) Low voltage / low power consumption design: 2.5~5.5V

## • Uses (BU9796FS)

Telephone, FAX, Portable equipments (POS, ECR, PDA etc.), DSC, DVC, Car audio, Home electrical appliance, Meter equipment etc.

|                               |        | ,              |        |                                                        |  |  |

|-------------------------------|--------|----------------|--------|--------------------------------------------------------|--|--|

| Parameter                     | Symbol | Limits         | Unit   | Remarks                                                |  |  |

| Power Supply Voltage1         | VDD    | -0.5 ~ +7.0    | V      | Power supply                                           |  |  |

| Power Supply Voltage2         | VLCD   | -0.5 ~ +7.0    | V      | LCD drive voltage                                      |  |  |

| Allowable loss                | Pd     | 0.64           | W      | When use more than Ta=25°C, subtract 6.4mW per degree. |  |  |

| Input voltage range           | VIN    | -0.5 ~ VDD+0.5 | V      |                                                        |  |  |

| Operational temperature range | Topr   | -40 ~ +85      | degree |                                                        |  |  |

| Storage temperature range     | Tstg   | -55 ~ +125     | degree |                                                        |  |  |

• Absolute Maximum Ratings (Ta=25degree, VSS=0V) (BU9796FS)

\*This product is not designed against radioactive ray.

## • Recommend operating conditions (Ta=25degree, VSS=0V) (BU9796FS)

| Parameter             | Symbol | MIN | TYP | MAX     | Unit | Remarks           |

|-----------------------|--------|-----|-----|---------|------|-------------------|

| Power Supply Voltage1 | VDD    | 2.5 | -   | 5.5     | V    | Power supply      |

| Power Supply Voltage2 | VLCD   | 0   | -   | VDD-2.4 | V    | LCD drive voltage |

\* Please use in the range of VDD-VLCD  $\geq$  2.4V

## • Electrical Characteristics (BU9796FS)

DC Characteristics (VDD=2.5~5.5V, VLCD=0V, VSS=0V, Ta=-40~85degree, unless otherwise specified)

| Parameter          |        | Quanta |        | Limit |         | 1.1  | Condition                                                                                                                                    |

|--------------------|--------|--------|--------|-------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                    |        | Symbol | MIN    | TYP   | MAX     | Unit | Condition                                                                                                                                    |

| "H" level input v  | oltage | VIH    | 0.7VDD | -     | VDD     | V    |                                                                                                                                              |

| "L" level input vo | oltage | VIL    | VSS    | -     | 0.3VDD  | V    |                                                                                                                                              |

| "H" level input c  | urrent | IIH    | -      | -     | 1       | uA   |                                                                                                                                              |

| "L" level input cu | urrent | ⊒      | -1     | -     | _       | uA   |                                                                                                                                              |

| LCD Driver SEG     |        | RON    | -      | 3     | -       | kΩ   | lload=±10uA                                                                                                                                  |

| on resistance      | COM    | RON    | -      | 3     | -       | kΩ   | lload-±10uA                                                                                                                                  |

| VLCD supply vo     | oltage | VLCD   | 0      | -     | VDD-2.4 | V    | VDD-VLCD 2.4V                                                                                                                                |

| Standby current    |        | IDD1   | -      | -     | 5       | uA   | Display off, Oscillation off                                                                                                                 |

| Power consumption  |        | IDD2   | -      | 12.5  | 30      | uA   | VDD=3.3V, VLCD=0V, Ta=25degree<br>Power save mode SR = Power save mode1,<br>Power save mode FR = Power save mode1<br>1/3 bias, Frame inverse |

| Frame freque       | ncy    | fCLK   | 56     | 80    | 104     | Hz   | Power save mode FR = Normal mode                                                                                                             |

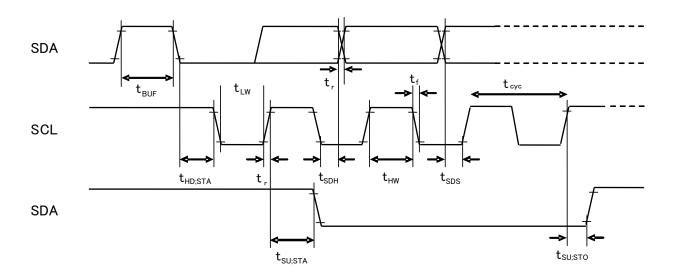

MPU interface Characteristics (VDD=2.5~5.5V, VLCD=0V, VSS=0V, Ta=-40~85degree, unless otherwise specified)

| Deremeter                  | Cumbal  | Limit |      |      | Linit | Condition |

|----------------------------|---------|-------|------|------|-------|-----------|

| Parameter                  | Symbol  | MIN.  | TYP. | MAX. | Unit  | Condition |

| Input rise time            | tr      | -     | -    | 0.3  | us    |           |

| Input fall time            | tf      | -     | -    | 0.3  | us    |           |

| SCL cycle time             | tSCYC   | 2.5   | -    | -    | us    |           |

| "H" SCL pulse width        | tSHW    | 0.6   | -    | -    | us    |           |

| "L" SCL pulse width        | tSLW    | 1.3   | -    | -    | us    |           |

| SDA setup time             | tSDS    | 100   | -    | -    | ns    |           |

| SDA hold time              | tSDH    | 100   | -    | -    | ns    |           |

| Buss free time             | tBUF    | 1.3   | -    | -    | us    |           |

| START condition hold time  | tHD;STA | 0.6   | -    | -    | us    |           |

| START condition setup time | tSU;STA | 0.6   | -    | -    | us    |           |

| STOP condition setup time  | tSU;STO | 0.6   | -    | -    | us    |           |

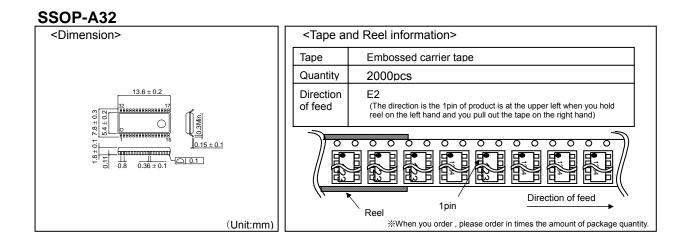

Fig. BU9796FS-1 interface timing

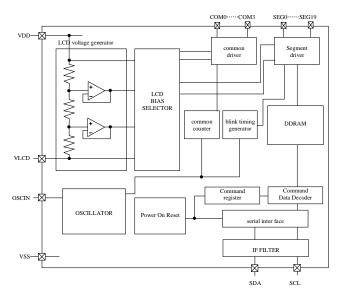

## •Block Diagram (BU9796FS)

Fig. BU9796FS-2 block diagram

• Pin Arrangement (BU9796FS)

Fig. BU9796FS-3 Pin arrangement

|          |                 | 0/  |                                                                                                                                             |

|----------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| Terminal | Terminal<br>No. | I/O | Function                                                                                                                                    |

| TEST1    | 26              | -   | Test input (ROHM use only)<br>Must be connect to VSS                                                                                        |

| TEST2    | 27              | Ι   | Test input (ROHM use only)<br>TEST2="L": POR circuit enable<br>TEST2="H": POR circuit disenable,<br>refer to "Cautions in Power ON/OFF"     |

| OSCIN    | 28              | Ι   | External clock input<br>Ext clock and Int clock can be changed by command.<br>Must be connect to VSS when use internal oscillation circuit. |

| SDA      | 30              | I/O | serial data in-out terminal                                                                                                                 |

| SCL      | 29              |     | serial data transfer clock                                                                                                                  |

| VSS      | 25              |     | GND                                                                                                                                         |

| VDD      | 24              |     | Power supply                                                                                                                                |

| VLCD     | 23              |     | Power supply for LCD driving                                                                                                                |

| SEG0-19  | 31,32<br>1-18   | 0   | SEGMENT output for LCD driving                                                                                                              |

| COM0-3   | 19-22           | 0   | COMMON output for LCD driving                                                                                                               |

## •Terminal description (BU9796FS)

## • Command Description (BU9796FS)

D7 (MSB) is bit for command or data judgment. Refer to Command and data transfer method.

- C: 0: Next byte is RAM write data.

- 1: Next byte is command.

## • Display control (DISCTL)

| MSB |    |    |    |    |    |    | LSB |   |

|-----|----|----|----|----|----|----|-----|---|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |   |

| С   | 0  | 1  | P4 | P3 | P2 | P1 | P0  | Ī |

## Set Power save mode FR

| Setup            | P4 | P3 | Reset initialize condition |

|------------------|----|----|----------------------------|

| Normal mode      | 0  | 0  | 0                          |

| Power save mode1 | 0  | 1  |                            |

| Power save mode2 | 1  | 0  |                            |

| Power save mode3 | 1  | 1  |                            |

### Set LCD drive waveform

| Setup           | P2 | Reset initialize condition |

|-----------------|----|----------------------------|

| Line inversion  | 0  | 0                          |

| Frame inversion | 1  |                            |

## Set Power save mode SR

| P1 | P0               | Reset initialize condition                                                      |

|----|------------------|---------------------------------------------------------------------------------|

| 0  | 0                |                                                                                 |

| 0  | 1                |                                                                                 |

| 1  | 0                | 0                                                                               |

| 1  | 1                |                                                                                 |

|    | 0<br>0<br>1<br>1 | 11         10           0         0           1         0           1         1 |

\* Please keep condition VDD-VLCD $\geq$  3.0V in High power mode.

### • Mode Set (MODE SET)

MOD

| MSB |    | -  | ,  |    |    |    | LSB      |         |

|-----|----|----|----|----|----|----|----------|---------|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0       |         |

| С   | 1  | 0  | *  | P3 | P2 | *  | *        |         |

|     |    |    |    |    |    | (  | *: Don'i | t Care) |

## Set display ON and OFF

| Setup       | P3 | Reset initialize condition |

|-------------|----|----------------------------|

| Display OFF | 0  | 0                          |

| Display ON  | 1  |                            |

### Set bias level

| Setup    | P3 | Reset initialize condition |

|----------|----|----------------------------|

| 1/3 Bias | 0  | 0                          |

| 1/2 Bias | 1  |                            |

Address set (ADSET)

| MSB                                                |    |    |    |    |    |    | LSB |   |

|----------------------------------------------------|----|----|----|----|----|----|-----|---|

| D7                                                 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |   |

| С                                                  | 0  | 0  | P4 | P3 | P2 | P1 | P0  | ĺ |

| The range of address can be get as 00000 to 10011/ |    |    |    |    |    |    |     |   |

The range of address can be set as 00000 to 10011(2).

## • Set IC Operation (ICSET)

| MSB |    |    |    |    |    |    | LSB     |         |

|-----|----|----|----|----|----|----|---------|---------|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0      |         |

| С   | 1  | 1  | 0  | 1  | *  | P1 | P0      |         |

|     |    |    |    |    |    | (  | *: Don' | t Care) |

Set software reset execution

| Setup                  | P1 |

|------------------------|----|

| No operation           | 0  |

| Software Reset execute | 1  |

Set oscillator mode

| setup                | P0 | Reset initialize condition |

|----------------------|----|----------------------------|

| Internal oscillation | 0  | 0                          |

| External clock input | 1  |                            |

• Blink control (BLKCTL)

| MSB |    |    |    |    |    |    | LSB     |         |

|-----|----|----|----|----|----|----|---------|---------|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0      |         |

| С   | 1  | 1  | 1  | 0  | *  | P1 | P0      |         |

|     |    |    |    |    |    | (  | *· Don' | t Care) |

(\*: Don't Care)

Set blink mode

| Blink mode (Hz) | P1 | P0 | Reset initialize condition |

|-----------------|----|----|----------------------------|

| OFF             | 0  | 0  | 0                          |

| 0.5             | 0  | 1  |                            |

| 1               | 1  | 0  |                            |

| 2               | 1  | 1  |                            |

• All Pixel control (APCTL)

| MSB |    | ,  | ,  |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| С   | 1  | 1  | 1  | 1  | 1  | P1 | P0  |

All display set ON, OFF

| APON         | P1 | Reset initialize condition |  |  |  |

|--------------|----|----------------------------|--|--|--|

| Normal       | 0  | 0                          |  |  |  |

| All pixel ON | 1  |                            |  |  |  |

| APOFF         | P0 | Reset initialize condition |  |  |  |

|---------------|----|----------------------------|--|--|--|

| Normal        | 0  | 0                          |  |  |  |

| All pixel OFF | 1  |                            |  |  |  |

• Function description (BU9796FS)

## • Command transfer method

1byte after Slave Address always becomes command input.

MSB ("command or data judge bit") of command decide to next data is command or display data. When set "command or data judge bit"='1', next byte will be command.

When set "command or data judge bit"='0', next byte data is display data.

|  | s | Slave address | А | 1 | Command | А | 1 | Command | А | 1 | Command | А | 0 | Command | А | Display Data |  | Ρ |

|--|---|---------------|---|---|---------|---|---|---------|---|---|---------|---|---|---------|---|--------------|--|---|

|--|---|---------------|---|---|---------|---|---|---------|---|---|---------|---|---|---------|---|--------------|--|---|

Once it becomes display data transfer condition, it cannot input command. When want to input command again, please generate "START condition" once.

## • Write display and transfer method

This device has Display Data RAM (DDRAM) of 50×4=200bit.

The relationship between data input and display data, DDRAM data and address are as follows; Slave address Command

|     | C             | lav | e audress | 5   |   | Comma  | na   |   |      |       |      |     |       |       |       |      |

|-----|---------------|-----|-----------|-----|---|--------|------|---|------|-------|------|-----|-------|-------|-------|------|

|     | S             | 01  | 111100    | А   | 0 | 000000 | A 00 | а | b c  | d e f | g h  | Aij | k I n | n n o | p A   | P    |

| חח  | DDRAM address |     |           |     |   |        |      |   |      |       |      |     |       |       |       |      |

| 001 |               | auu | 1033      |     |   |        |      |   |      |       |      |     |       |       |       |      |

|     | 00            | )   | 01        | 02  |   | 03     | 04   |   | 05   | 06    | 07   | ••• | 2Fh   | 30h   | 31h   | _    |

| 0   | а             |     | е         | i   |   | m      |      |   |      |       |      |     |       |       |       | COM0 |

| _ 1 | b             |     | f         | j   |   | n      |      |   |      |       |      |     |       |       |       | COM1 |

| 2   | С             |     | g         | k   |   | 0      |      |   |      |       |      |     |       |       |       | COM2 |

| 3   | d             |     | h         | Ι   |   | р      |      |   |      |       |      |     |       |       |       | COM3 |

|     | SEG           | 60  | SEG1      | SEG | 2 | SEG3   | SEG4 |   | SEG5 | SEG6  | SEG7 |     | SEG47 | SEG48 | SEG49 | -    |

Data transfer to DDRAM happens every 4bit data. So It will be finished to transfer with no need to wait ACK.

## Reset initialize condition

BIT

Initial condition after execute Software Reset is as follows.

- Display is OFF.

- DDRAM address is initialized (DDRAM Data is not initialized).

- Refer to Command Description about initialize value of register.

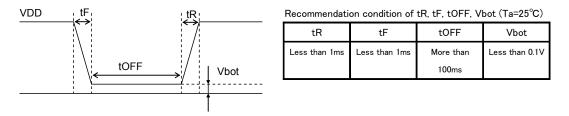

• Cautions in Power ON/OFF (BU9796FS)

This device has "P.O.R" (Power-On Reset) circuit and Software Reset function. Please keep the following recommended Power-On conditions in order to power up properly.

Please set power up conditions to meet the recommended tR, tF, tOFF, and Vbot spec below in order to ensure P.O.R operation

\* It has to set TEST2="L" to be valid in POR circuit.

Fig. BU9796FS-4 Power ON/OFF waveform

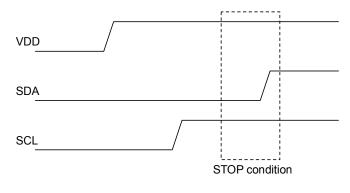

If it is difficult to meet above conditions, execute the following sequence after Power-On.

- \* It has to keep the following sequence in the case of TEST2="H". As POR circuit is invalid status. But it is not able to accept Command input in Power off status, it has to take care that software reset is not perfectly alternative method of POR function.

- (1) Generate STOP condition

Fig. BU9796FS-5 Stop condition

- (2) Generate START condition.

- (3) Issue slave address

- (4) Execute Software Reset (ICSET) command

### • Cautions on use

#### (1) Absolute Maximum Ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down devices, thus making impossible to identify breaking mode such as a short circuit or an open circuit. If any special mode exceeding the absolute maximum ratings is assumed, consideration should be given to take physical safety measures including the use of fuses, etc.

#### (2) Operating conditions

These conditions represent a range within which characteristics can be provided approximately as expected. The electrical characteristics are guaranteed under the conditions of each parameter.

#### (3) Reverse connection of power supply connector

The reverse connection of power supply connector can break down ICs. Take protective measures against the breakdown due to the reverse connection, such as mounting an external diode between the power supply and the IC's power supply terminal.

#### (4) Power supply line

Design PCB pattern to provide low impedance for the wiring between the power supply and the GND lines. In this regard, or the digital block power supply and the analog block power supply, even though these power supplies has the same level of potential, separate the power supply pattern for the digital block from that for the analog block, thus suppressing the diffraction of digital noises to the analog block power supply resulting from impedance common to the wiring patterns. For the GND line, give consideration to design the patterns in a similar manner. Furthermore, for all power supply terminals to ICs, mount a capacitor between the power supply and the GND terminal. At the same time, in order to use an electrolytic capacitor, thoroughly check to be sure the characteristics of the capacitor to be used present no problem including the occurrence of capacity dropout at a low temperature, thus determining the constant.

#### (5) GND voltage

Make setting of the potential of the GND terminal so that it will be maintained at the minimum in any operating state. Furthermore, check to be sure no terminals are at a potential lower than the GND voltage including an actual electric transient.

#### (6) Short circuit between terminals and erroneous mounting

In order to mount ICs on a set PCB, pay thorough attention to the direction and offset of the ICs. Erroneous mounting can break down the ICs. Furthermore, if a short circuit occurs due to foreign matters entering between terminals or between the terminal and the power supply or the GND terminal, the ICs can break down.

#### (7) Operation in strong electromagnetic field

Be noted that using ICs in the strong electromagnetic field can malfunction them.

#### (8) Inspection with set PCB

On the inspection with the set PCB, if a capacitor is connected to a low-impedance IC terminal, the IC can suffer stress. Therefore, be sure to discharge from the set PCB by each process. Furthermore, in order to mount or dismount the set PCB to/from the jig for the inspection process, be sure to turn OFF the power supply and then mount the set PCB to the jig. After the completion of the inspection, be sure to turn OFF the power supply and then dismount it from the jig. In addition, for protection against static electricity, establish a ground for the assembly process and pay thorough attention to the transportation and the storage of the set PCB.

#### (9) Input terminals

In terms of the construction of IC, parasitic elements are inevitably formed in relation to potential. The operation of the parasitic element can cause interference with circuit operation, thus resulting in a malfunction and then breakdown of the input terminal. Therefore, pay thorough attention not to handle the input terminals, such as to apply to the input terminals a voltage lower than the GND respectively, so that any parasitic element will operate. Furthermore, do not apply a voltage to the input terminals when no power supply voltage is applied to the IC. In addition, even if the power supply voltage is applied, apply to the input terminals a voltage lower than the power supply voltage or within the guaranteed value of electrical characteristics.

#### (10) Ground wiring pattern

If small-signal GND and large-current GND are provided, It will be recommended to separate the large-current GND pattern from the small-signal GND pattern and establish a single ground at the reference point of the set PCB so that resistance to the wiring pattern and voltage fluctuations due to a large current will cause no fluctuations in voltages of the small-signal GND. Pay attention not to cause fluctuations in the GND wiring pattern of external parts as well.

#### (11) External capacitor

In order to use a ceramic capacitor as the external capacitor, determine the constant with consideration given to a degradation in the nominal capacitance due to DC bias and changes in the capacitance due to temperature, etc.

#### (12) No Connecting input terminals

In terms of extremely high impedance of CMOS gate, to open the input terminals causes unstable state. And unstable state brings the inside gate voltage of p-channel or n-channel transistor into active. As a result, battery current may increase. And unstable state can also causes unexpected operation of IC. So unless otherwise specified, input terminals not being used should be connected to the power supply or GND line.

#### (13) Rush current

When power is first supplied to the CMOS IC, it is possible that the internal logic may be unstable and rush current may flow instantaneously. Therefore, give special condition to power coupling capacitance, power wiring, width of GND wiring, and routing of connections.

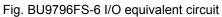

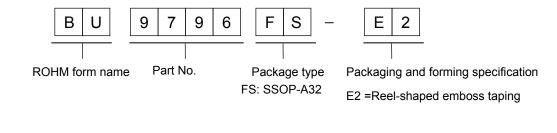

Order form name selection

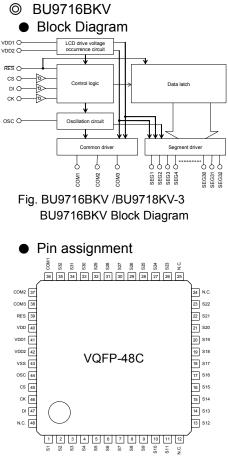

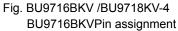

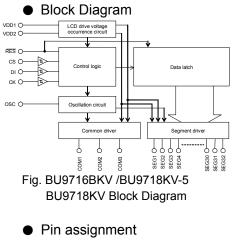

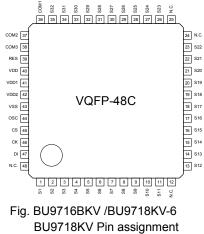

# BU9716BKV/BU9718KV 96SEGMENT (32SEG×3COM) Driver

Features (BU9716BKV/BU9718KV)

1) LCD driving port : 3 Common output, 32 Segment output

- 2) Display duty: 1/3duty

- 3) Each 1/2 or 1/3 can be selected for power supply for LCD display.

- Uses (BU9716BKV/BU9718KV) Portable equipments (POS, ECR, PDA etc.) DSC, DSC, Telephone etc.

• Line up (BU9716BKV/BU9718KV)

| Parameter                     | BU9716BKV | BU9718KV |

|-------------------------------|-----------|----------|

| Recommended operating voltage | 4.5~5.5V  | 2.7~3.5V |

| Package                       | VQFP-48C  | VQFP-48C |

ABSOLUTE MAXIMUM RATINGS (Ta=25degree, Vss=0V) (BU9716BKV/BU9718KV)

| Parameter                 | Symbol | Pin              | Ratings      | Unit   |

|---------------------------|--------|------------------|--------------|--------|

| Maximum Supply Voltage    | VDD    | VDD              | -0.3~+7.0    | V      |

| Input Voltage             | VIN    | OSC,CS,CK,DI,RES | -0.3~VDD+0.3 | V      |

| Output Voltage            | VOUT   | OSC              | -0.3~VDD+0.3 | V      |

| Output Current            | ISO    | S1~S32           | 300          | mA     |

| Output Current            | ICO    | COM1~COM3        | 3            | mA     |

| Power Dissipation         | Pd     | _                | 400          | mW     |

| Storage Temperature Range | Tstg   | _                | -55~+125     | degree |

Note: Derating decreases at -4mW/degree for operation above Ta=25degree.

## RECOMMENDED OPERATING CONDITIONS

## **© BU9716BKV**

| Parameter             | Symbol | Pin  | MIN  | TYP    | MAX  | Unit   |

|-----------------------|--------|------|------|--------|------|--------|

| Supply Voltage        | VDD    | VDD  | +4.5 |        | +5.5 | V      |

| Input Voltaga         | VDD1   | VDD1 | 0    | 2/3VDD | VDD  | V      |

| Input Voltage         | VDD2   | VDD2 | 0    | 1/3VDD | VDD  | V      |

| Operating Temperature | Topr   | —    | -40  |        | +85  | degree |

**© BU9718KV**

| Parameter                      | Symbol | Pin  | MIN  | TYP    | MAX  | Unit   |

|--------------------------------|--------|------|------|--------|------|--------|

| Supply Voltage                 | VDD    | VDD  | +2.7 | -      | +3.5 | V      |

| Input Voltage                  | VDD1   | VDD1 | 0    | 2/3VDD | VDD  | V      |

| Input Voltage                  | VDD2   | VDD2 | 0    | 1/3VDD | VDD  | V      |

| External Input wave frequency  | fOSC   | OSC  | -    | 38     | 100  | kHz    |

| Recommended external resistor  | R      | OSC  | -    | 47     | -    | kΩ     |

| Recommended external capacitor | С      | OSC  | -    | 1000   | -    | pF     |

| Operating Temperature          | Topr   | —    | -40  | -      | +85  | degree |

\* This product is not designed to be protected against radiation.

## • ERECTRICAL CHARACTERISTICS

| $\odot$ | BU9716BKV | (VDD=4.5V-5.5V, | Ta=25degree) |

|---------|-----------|-----------------|--------------|

|---------|-----------|-----------------|--------------|

| Parameter                      | Symbol | Pin          | Condition      | MIN    | TYP     | MAX    | Unit |

|--------------------------------|--------|--------------|----------------|--------|---------|--------|------|

| "H" Level Input Voltage        | VIH    | CS,CK,DI,RES |                | 0.8VDD | -       | VDD    | V    |

| "L" Level Input Voltage        | VIL    | CS,CK,DI,RES |                | 0      | -       | 0.2VDD | V    |

| "H" Level Input Current        | IIH    | CS,CK,DI,RES | VI=VDD         | 0      | -       | 6.0    | uA   |

| "L" Level Input Current        | IIL    | CS,CK,DI,RES | VI=VSS         | 0      | -       | 6.0    | uA   |

| "H" Level Output Voltage       | VSOH   | S1~S32       | IO=-20mA       | -      | VDD-1.0 | -      | V    |

|                                | VCOH   | COM1~COM3    | IO=-100mA      | -      | VDD-1.0 | -      | V    |

| "L" Level Output Voltage       | VSOL   | S1~S32       | IO=20mA        | -      | 1.0     | -      | V    |

|                                | VCOL   | COM1~COM3    | IO=100mA       | -      | 1.0     | -      | V    |

|                                | VCM1   | COM1~COM3    | 1/2bias        | -      | 1/2 VDD | -      | V    |

|                                | VSM1   | S1~S32       | 1/3bias        | -      | 2/3 VDD | -      | V    |

| Center-Level Output<br>Voltage | VCM2   | COM1~COM3    | 1/3bias        | -      | 2/3 VDD | -      | V    |

|                                | VSM2   | S1~S32       | 1/3bias        | -      | 1/3 VDD | -      | V    |

|                                | VCM3   | COM1~COM3    | 1/3bias        | -      | 1/3 VDD | -      | V    |

| Supply Current                 | IQ     |              | Low Power Mode | -      | 30      | 70     | uA   |

| Supply Current                 | IDD    |              | fOSC=38kHz     | -      | 200     | 500    | uA   |

## BU9718KV (VDD=2.7-3.5V, Ta=25degree)

| Parameter                      | Symbol | Pin          | Condition      | MIN    | TYP     | MAX    | Unit |

|--------------------------------|--------|--------------|----------------|--------|---------|--------|------|

| "H" level Input Voltage        | VIH    | CS,CK,DI,RES |                | 0.8VDD | -       | VDD    | V    |

| "L" Level Input Voltage        | VIL    | CS,CK,DI,RES |                | 0      | -       | 0.2VDD | V    |

| "H" Level Input Current        | IIH    | CS,CK,DI,RES | VI=VDD         | 0      | -       | 6.0    | uA   |

| "L" Level Input Current        | IIL    | CS,CK,DI,RES | VI=VSS         | 0      | -       | 6.0    | uA   |

|                                | VSOH   | S1~S32       | IO=-20mA       | -      | VDD-1.0 | -      | V    |

| "H" Level Output Voltage       | VCOH   | COM1~COM3    | IO=-100mA      | -      | VDD-1.0 | -      | V    |

|                                | VSOL   | S1~S32       | IO=20mA        | -      | 1.0     | -      | V    |

| "L" Level Output Voltage       | VCOL   | COM1~COM3    | IO=100mA       | -      | 1.0     | -      | V    |

|                                | VCM1   | COM1~COM3    | 1/2bias        | -      | 1/2 VDD | -      | V    |

|                                | VSM1   | S1~S32       | 1/3bias        | -      | 2/3 VDD | -      | V    |

| Center-Level Output<br>Voltage | VCM2   | COM1~COM3    | 1/3bias        | -      | 2/3 VDD | -      | V    |

| Voltage                        | VSM2   | S1~S32       | 1/3bias        | -      | 1/3 VDD | -      | V    |

|                                | VCM3   | COM1~COM3    | 1/3bias        | -      | 1/3 VDD | -      | V    |

| Supply Current                 | IQ     |              | Low Power Mode | -      | 0.1     | 30     | uA   |

| Supply Current                 | IDD    |              | fOSC=38kHz     | -      | 100     | 300    | uA   |

## AC ERECTRICAL CHARACTERISTICS

## BU9716BKV (VDD=4.5-5.5V, Ta=25degree)

| Parameter                             | Symbol | Pin      | MIN | TYP  | MAX | Unit |

|---------------------------------------|--------|----------|-----|------|-----|------|

| Recommended External Resistance       | R      | OSC      | -   | 47   | -   | kΩ   |

| Recommended External Capacitance      | С      | OSC      | -   | 1000 | -   | pF   |

| Oscillator frequency guaranteed range | fOSC   | OSC      | 19  | 38   | 76  | kHz  |

| Data Setup Time                       | tDS    | CK,DI    | 100 | -    | -   | ns   |

| Data Hold Time                        | tDH    | CK,DI    | 100 | -    | -   | ns   |

| CS Setup Time                         | tCS    | CS,CK    | 100 | -    | -   | ns   |

| CS Hold Time                          | tCH    | CS,CK    | 100 | -    | -   | ns   |

| CK High-Level Pulse width             | tCKH   | СК       | 100 | -    | -   | ns   |

| CK Low-Level Pulse width              | tCKL   | СК       | 100 | -    | -   | ns   |

| Rise Time                             | tr     | CS,CK,DI | -   | -    | 300 | ns   |

| Fall Time                             | tf     | CS,CK,DI | -   | -    | 300 | ns   |

## BU9718KV (VDD=2.7V-3.5V, Ta=25degree)

| Parameter                             | Symbol | Pin      | MIN | TYP | MAX | Unit | Condition           |

|---------------------------------------|--------|----------|-----|-----|-----|------|---------------------|

| Oscillator frequency guaranteed range | fOSC   | OSC      | 10  | 38  | 80  | kHz  | R=47kΩ,C=1000pF     |

| Operating frequency                   | fOSC   | OSC      | -   | -   | 100 | kHz  | External Input case |

| Data Setup Time                       | tDS    | CK,DI    | 200 | -   | -   | ns   |                     |

| Data Hold Time                        | tDH    | CK,DI    | 200 | -   | -   | ns   |                     |

| CS Setup Time                         | tCS    | CS,CK    | 200 | -   | -   | ns   |                     |

| CS Hold Time                          | tCH    | CS,CK    | 200 | -   | -   | ns   |                     |

| CK High-Level Pulse width             | tCKH   | СК       | 200 | -   | -   | ns   |                     |

| CK Low-Level Pulse width              | tCKL   | СК       | 200 | -   | -   | ns   |                     |

| Rise Time                             | tr     | CS,CK,DI | -   | -   | 100 | ns   |                     |

| Fall Time                             | tf     | CS,CK,DI | -   | -   | 100 | ns   |                     |

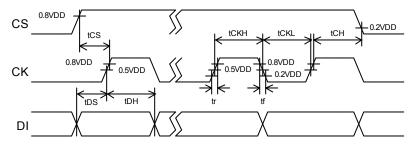

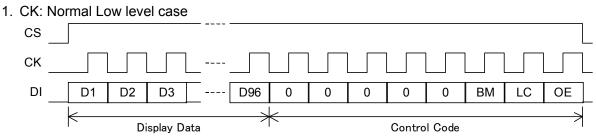

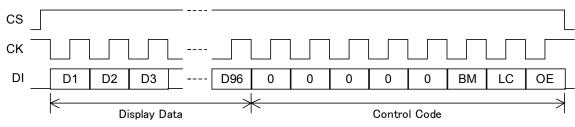

Fig. BU9716BKV/BU9718KV-2 CK: Normal Low Level case

Fig. BU9716BKV/BU9718KV-3 CK: Normal High Level case

## BU9718KV BU9718KV State St

## Terminal description

| Pin No,                | Terminal             | I/O | Description                                                                                                                          | Unused |

|------------------------|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1-11<br>13-23<br>26-35 | S1-S32               | 0   | Segment output pins. It output the<br>proper LCD voltage levels<br>corresponding to the input data<br>multiplexed with COM1 to CPM3. | OPEN   |

| 36<br>37<br>38         | COM1<br>COM2<br>COM3 | 0   | Common driver output pins.<br>Frame frequency:<br>fO=(fOSC/384) Hz                                                                   | OPEN   |

| 39                     | RES                  | I   | Active low reset input. Used for<br>resetting all latches.<br>(Include Control Code.)                                                | VDD    |

| 44                     | OSC                  | -   | Internal Oscillator connection for<br>an external resister and capacitor<br>which determines fOSC.                                   | VSS    |

| 45                     | CS                   | Ι   | Chip select. Used for serial data transfer. Active high.                                                                             | VSS    |

| 46                     | СК                   | Ι   | Input data clock. Used for serial<br>data transfer.                                                                                  | VSS    |

| 47                     | DI                   | Ι   | Data input. Used for serial data transfer.                                                                                           | VSS    |

| 41                     | VDD1                 | -   | Internal voltage reference<br>connection.<br>Connect to VDD2 at 1/2 bias<br>mode.                                                    | OPEN   |

| 42                     | VDD2                 | -   | Internal voltage reference<br>connection.<br>Connect to VDD1 at 1/2 bias<br>mode.                                                    | OPEN   |

## • Terminal description

| Pin<br>No,             | Terminal             | I/O | Description                                                                                                                          | Unused |

|------------------------|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1-11<br>13-23<br>26-35 | S1-S32               | 0   | Segment output pins. It output the<br>proper LCD voltage levels<br>corresponding to the input data<br>multiplexed with COM1 to CPM3. | OPEN   |

| 36<br>37<br>38         | COM1<br>COM2<br>COM3 | 0   | Common driver output pins.<br>Frame frequency: fO= (fOSC/<br>384) Hz                                                                 | OPEN   |

| 39                     | RES                  | I   | Active low reset input. Used for resetting all latches. (Include Control Code.)                                                      | VDD    |

| 44                     | OSC                  | -   | Internal Oscillator connection for<br>an external resister and capacitor<br>which determines fOSC.                                   | VSS    |

| 45                     | CS                   | I   | Chip select. Used for serial data transfer. Active high.                                                                             | VSS    |

| 46                     | СК                   | I   | Input data clock. Used for serial data transfer.                                                                                     | VSS    |

| 47                     | DI                   | I   | Data input. Used for serial data transfer.                                                                                           | VSS    |

| 41                     | VDD1                 | -   | Internal voltage reference<br>connection.<br>Connect to VDD2 at 1/2 bias<br>mode.                                                    | OPEN   |

| 42                     | VDD2                 | -   | Internal voltage reference<br>connection.<br>Connect to VDD1 at 1/2 bias<br>mode.                                                    | OPEN   |

## • Timing chart

## © Command / data Input

## 2. CK: Normal High level case

Data transfer is enabled when CS is asserted high. The value of DI is shifted into the shift register on the rising edge of CK. After all of the data in DI is sifted in, CS must be asserted low. The new display data and control code takes effect after the falling edge of CS.

## O Control Code

| -  |                                                                    |

|----|--------------------------------------------------------------------|

| OE | Output-Enable Control                                              |

| 0  | Normal Operation                                                   |

| 1  | Blank Display-as if all display data =0(Oscillator is active.)     |

|    |                                                                    |

| LC | Low-power Mode Control                                             |

| 0  | Normal Operation                                                   |

| 1  | Low-power Mode: Oscillator is stopped, segment /common outputs="L" |

|    |                                                                    |

| BM | Bias Mode Control                                                  |

| 0  | 1/3 Bias                                                           |

## O DISPLAY DATA

1

1/2 Bias

| SEGMENT | COM3 | COM2 | COM1 | SEGMENT | COM3 | COM2 | COM1 |

|---------|------|------|------|---------|------|------|------|

| S1      | D1   | D2   | D3   | S17     | D49  | D50  | D51  |

| S2      | D4   | D5   | D6   | S18     | D52  | D53  | D54  |

| S3      | D7   | D8   | D9   | S19     | D55  | D56  | D57  |

| S4      | D10  | D11  | D12  | S20     | D58  | D59  | D60  |

| S5      | D13  | D14  | D15  | S21     | D61  | D62  | D63  |

| S6      | D16  | D17  | D18  | S22     | D64  | D65  | D66  |

| S7      | D19  | D20  | D21  | S23     | D67  | D68  | D69  |

| S8      | D22  | D23  | D24  | S24     | D70  | D71  | D72  |

| S9      | D25  | D26  | D27  | S25     | D73  | D74  | D75  |

| S10     | D28  | D29  | D30  | S26     | D76  | D77  | D78  |

| S11     | D31  | D32  | D33  | S27     | D79  | D80  | D81  |

| S12     | D34  | D35  | D36  | S28     | D82  | D83  | D84  |

| S13     | D37  | D38  | D39  | S29     | D85  | D86  | D87  |

| S14     | D40  | D41  | D42  | S30     | D88  | D89  | D90  |

| S15     | D43  | D44  | D45  | S31     | D91  | D92  | D93  |

| S16     | D46  | D47  | D48  | S32     | D94  | D95  | D96  |

### Cautions on use

#### (1) Absolute Maximum Ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down devices, thus making impossible to identify breaking mode such as a short circuit or an open circuit. If any special mode exceeding the absolute maximum ratings is assumed, consideration should be given to take physical safety measures including the use of fuses, etc.

#### (2) Operating conditions

These conditions represent a range within which characteristics can be provided approximately as expected. The electrical characteristics are guaranteed under the conditions of each parameter.

#### (3) Reverse connection of power supply connector

The reverse connection of power supply connector can break down ICs. Take protective measures against the breakdown due to the reverse connection, such as mounting an external diode between the power supply and the IC's power supply terminal.

#### (4) Power supply line

Design PCB pattern to provide low impedance for the wiring between the power supply and the GND lines. In this regard, or the digital block power supply and the analog block power supply, even though these power supplies has the same level of potential, separate the power supply pattern for the digital block from that for the analog block, thus suppressing the diffraction of digital noises to the analog block power supply resulting from impedance common to the wiring patterns. For the GND line, give consideration to design the patterns in a similar manner. Furthermore, for all power supply terminals to ICs, mount a capacitor between the power supply and the GND terminal. At the same time, in order to use an electrolytic capacitor, thoroughly check to be sure the characteristics of the capacitor to be used present no problem including the occurrence of capacity dropout at a low temperature, thus determining the constant.

#### (5) GND voltage

Make setting of the potential of the GND terminal so that it will be maintained at the minimum in any operating state. Furthermore, check to be sure no terminals are at a potential lower than the GND voltage including an actual electric transient.

#### (6) Short circuit between terminals and erroneous mounting

In order to mount ICs on a set PCB, pay thorough attention to the direction and offset of the ICs. Erroneous mounting can break down the ICs. Furthermore, if a short circuit occurs due to foreign matters entering between terminals or between the terminal and the power supply or the GND terminal, the ICs can break down.

#### (7) Operation in strong electromagnetic field

Be noted that using ICs in the strong electromagnetic field can malfunction them.

#### (8) Inspection with set PCB

On the inspection with the set PCB, if a capacitor is connected to a low-impedance IC terminal, the IC can suffer stress. Therefore, be sure to discharge from the set PCB by each process. Furthermore, in order to mount or dismount the set PCB to/from the jig for the inspection process, be sure to turn OFF the power supply and then mount the set PCB to the jig. After the completion of the inspection, be sure to turn OFF the power supply and then dismount it from the jig. In addition, for protection against static electricity, establish a ground for the assembly process and pay thorough attention to the transportation and the storage of the set PCB.

#### (9) Input terminals

In terms of the construction of IC, parasitic elements are inevitably formed in relation to potential. The operation of the parasitic element can cause interference with circuit operation, thus resulting in a malfunction and then breakdown of the input terminal. Therefore, pay thorough attention not to handle the input terminals, such as to apply to the input terminals a voltage lower than the GND respectively, so that any parasitic element will operate. Furthermore, do not apply a voltage to the input terminals when no power supply voltage is applied to the IC. In addition, even if the power supply voltage is applied, apply to the input terminals a voltage lower than the power supply voltage or within the guaranteed value of electrical characteristics.

#### (10) Ground wiring pattern

If small-signal GND and large-current GND are provided, It will be recommended to separate the large-current GND pattern from the small-signal GND pattern and establish a single ground at the reference point of the set PCB so that resistance to the wiring pattern and voltage fluctuations due to a large current will cause no fluctuations in voltages of the small-signal GND. Pay attention not to cause fluctuations in the GND wiring pattern of external parts as well.

#### (11) External capacitor

In order to use a ceramic capacitor as the external capacitor, determine the constant with consideration given to a degradation in the nominal capacitance due to DC bias and changes in the capacitance due to temperature, etc.

#### (12) No Connecting input terminals

In terms of extremely high impedance of CMOS gate, to open the input terminals causes unstable state. And unstable state brings the inside gate voltage of p-channel or n-channel transistor into active. As a result, battery current may increase. And unstable state can also causes unexpected operation of IC. So unless otherwise specified, input terminals not being used should be connected to the power supply or GND line.

#### (13) Rush current

When power is first supplied to the CMOS IC, it is possible that the internal logic may be unstable and rush current may flow instantaneously. Therefore, give special condition to power coupling capacitance, power wiring, width of GND wiring, and routing of connections.

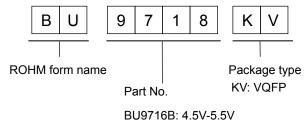

Order form name selection

BU9718: 2.7V-3.5V

## VQFP48C

- The contents described herein are correct as of June, 2008

- The contents described herein are subject to change without notice. For updates of the latest information, please contact and confirm with ROHM CO. LTD.

- Any part of this application note must not be duplicated or copied without our permission. upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams and information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or otherwise dispose of the same, implied right or license to practice or commercially exploit any intellectual property rights or other proprietary rights owned or controlled by ROHM CO., LTD. is granted to any such buyer. • The products described herein utilize silicon as the main material.

- The products described herein are not designed to be X ray proof.

- The products listed in this catalog are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

#### bout the products. Conta

Excellence in Electronics

## ROHM CO., LTD.

21, Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan TEL: +81-75-311-2121 FAX: +81-75-315-0172 URL http://www.rohm.com

| Published by                |

|-----------------------------|

| LSI Business Promotion Dept |

| Contact        | us for further info    | ormation about t      |

|----------------|------------------------|-----------------------|

| San Diego      | TEL: +1-858-625-3630   | FAX: +1-858-625-3670  |

| Atlanta        | TEL: +1-770-754-5972   | FAX: +1-770-754-0691  |

| Boston         | TEL: +1-978-371-0382   | FAX: +1-928-438-7164  |

| Chicago        | TEL: +1-847-368-1006   | FAX: +1-847-368-1008  |

| Dallas         | TEL: +1-469-287-5366   | FAX: +1-469-362-7973  |

| Denver         | TEL: +1-303-708-0908   | FAX: +1-303-708-0858  |

| Detroit        | TEL: +1-248-348-9920   | FAX: +1-248-348-9942  |

| Nashville      | TEL: +1-615-620-6700   | FAX: +1-615-620-6702  |

| Mexico         | TEL: +52-33-3123-2001  | FAX: +52-33-3123-2002 |

| Düsseldorf     | TEL: +49-2154-9210     | FAX: +49-2154-921400  |

| Munich         | TEL: +49-8161-48310    | FAX: +49-8161-483120  |

| Stuttgart      | TEL: +49-711-72723710  | FAX: +49-711-72723720 |

| France         | TEL: +33-1-5697-3060   | FAX: +33-1-5697-3080  |

| United Kingdom |                        | FAX: +44-1-908-235788 |

| Denmark        | TEL: +45-3694-4739     | FAX: +45-3694-4789    |

| Barcelona      | TEL: +34-9375-24320    | FAX: +34-9375-24410   |

| Hungary        | TEL: +36-1-4719338     | FAX: +36-1-4719339    |

| Poland         | TEL: +48-22-5757213    | FAX: +48-22-5757001   |

| Russia         | TEL: +7-95-980-6755    | FAX: +7-95-937-8290   |

| Seoul          | TEL: +82-2-8182-700    | FAX: +82-2-8182-715   |

| Masan          | TEL: +82-55-240-6234   | FAX: +82-55-240-6236  |

| Dalian         | TEL: +86-411-8230-8549 |                       |

| Beijing        | TEL: +86-10-8525-2483  | FAX: +86-10-8525-2489 |

| Tianjin        | TEL: +86-22-23029181   | FAX: +86-22-23029183  |

Shanghai Hangzhou Nanjing Ningbo Qingdao Suzhou Wuxi Shenzhen Dongguan Fuzhou Guangzhou Huizhou Xiamen Zhuhai Hong Kong Taipei Kaohsiung Kaohsiung Singapore Philippines Thailand Kuala Lumpur Penang Kyoto Yokohama

| TEL: +86-21-6279-2727  | FAX: +86-21-6247-2066  |

|------------------------|------------------------|

| TEL: +86-571-87658072  | FAX: +86-571-87658071  |

| TEL: +86-25-8689-0015  | FAX: +86-25-8689-0393  |

| TEL: +86-574-87654201  | FAX: +86-574-87654208  |

| TEL: +86-532-5779-312  | FAX:+86-532-5779-653   |

| TEL: +86-512-6807-1300 | FAX: +86-512-6807-2300 |

| TEL: +86-510-82702693  | FAX: +86-510-82702992  |

| TEL: +86-755-8307-3008 | FAX: +86-755-8307-3003 |

| TEL: +86-769-8393-3320 | FAX: +86-769-8398-4140 |

| TEL: +86-591-8801-8698 | FAX: +86-591-8801-8690 |

| TEL: +86-20-8364-9796  | FAX: +86-20-8364-9707  |

| TEL: +86-752-205-1054  | FAX: +86-752-205-1059  |

| TEL: +86-592-238-5705  | FAX: +86-592-239-8380  |

| TEL: +86-756-3232-480  | FAX: +86-756-3232-460  |

| TEL: +852-2-740-6262   | FAX: +852-2-375-8971   |

| TEL: +886-2-2500-6956  | FAX: +886-2-2503-2869  |