# **Programmable Temperature Controlled MOSFET Driver**

### **ISL25700**

The Temperature Controlled MOSFET Driver is a highly integrated solution that combines a MOSFET driver with overcurrent protection and two 8-bit resolution DACs on a monolithic CMOS integrated circuit (IC).

The ISL25700 sets up and monitors temperature at the point of interest, compares it with the user programmable setpoint, and adjusts the output until the set temperature is reached. An external power MOSFET, a heater, an NTC thermistor and the ISL25700 are parts of the temperature control loop.

It also features programmable overcurrent protection of the MOSFET. The current protection automatically adjusts the output voltage in order to keep MOSFET power under user defined limits. The protection settings always override the temperature settings that cause violation of the current limit.

There is an additional 8-bit General Purpose DAC that is available for application specific use.

The ISL25700 can be used in a variety of applications where constant temperature is a key parameter.

### **Applications**\*(see page 17)

- Oven Controlled Applications with Micro Temperature Chamber in:

- Basestations

- Spectrometers

- Precision Meters

- Precision Generators

### **Features**

- User-programmable Setpoint via I<sup>2</sup>C Serial Interface

- Setpoint Temperature Range from +40°C to +110°C

- Operational Temperature Range from -40°C to +125°C

- 3°C Initial Setpoint Accuracy

- Coarse and Fine Tuning Setpoint Control

- +15°C Coarse Adjustment

- +0.1°C Fine Adjustment

- ±0.5°C Long-term Drift Error

- Programmable Current Protection of External MOSFET

- 5-bit Selectable Gain Control

- Wide Power Supply Range: 3V to 15V

- Works with  $20k\Omega$  to  $200k\Omega$  External NTC Thermistor

- General Purpose 8-bit DAC 0.4% Output Resolution

- High Reliability

- Endurance: 10,000 Data Changes per Bit per Register

- Register Data Retention: 10 years @ T ≤ +125°C

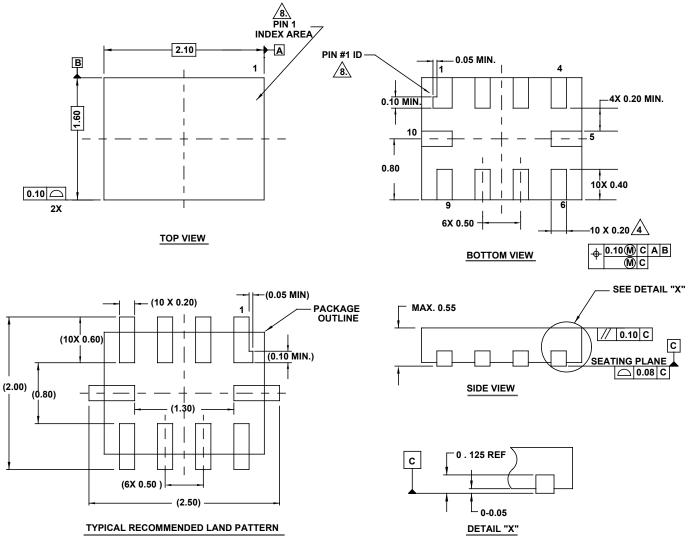

- 10 Lead µTQFN 2.1mmx1.6mm Package

- Pb-free (RoHS Compliant)

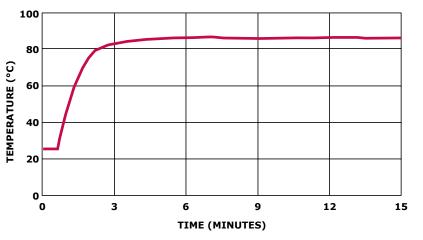

FIGURE 1. TYPICAL TEMPERATURE SETTLING TIME

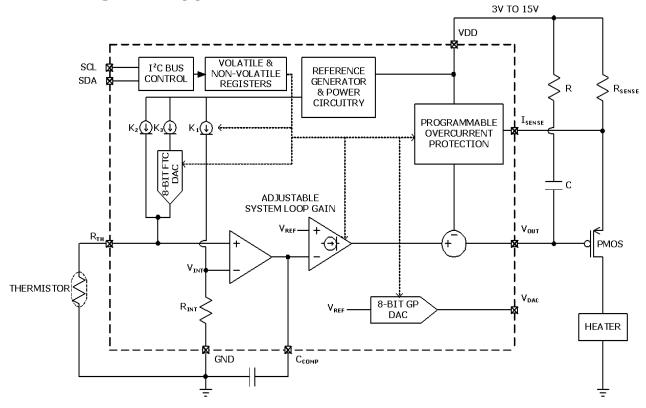

### **Block Diagram/Application Circuit**

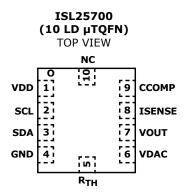

### **Pin Configuration**

## **Pin Descriptions**

| µTQFN PIN | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | VDD             | Power supply. This pins supplies the power necessary to operate the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2         | SCL             | $I^2C$ interface input clock. This input is the serial clock of the $I^2C$ serial interface. SCL requires an external pull-up resistor. It has an internal pull-down resistor of ${\sim}3M\Omega$ to prevent a floating input if the pin will be left unconnected.                                                                                                                                                                                                                                                                                                  |

| 3         | SDA             | Open Drain Serial Data Input/Output for the I <sup>2</sup> C interface. The SDA is a bidirectional serial data input/output pin for I <sup>2</sup> C interface. It receives device address, operation code and data from an I <sup>2</sup> C external master device at the rising edge of the serial clock SCL, and it shifts out data after each falling edge of the serial clock.<br>The SDA pin requires an external pull-up resistor. It has an internal pull-down resistor of $\sim 3M\Omega$ to prevent a floating input if the pin will be left unconnected. |

| 4         | GND             | Ground. Bias and reference ground of the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5         | R <sub>TH</sub> | External NTC thermistor. An external NTC thermistor makes one shoulder of the Wheatstone bridge and must be connected between the $R_{TH}$ pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6         | VDAC            | DAC Output. This is the output of the precision 8-bit DAC. Default DAC output is in the range of 0V to 2V. The DAC output range can be extended with a gain of 2 by setting the DAC Gain bit.                                                                                                                                                                                                                                                                                                                                                                       |

| 7         | VOUT            | Output voltage that controls an external P-MOSFET. This pin drives an external P-MOSFET proportional to unbalanced condition of the Wheatstone bridge.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8         | ISENSE          | Current Sense input. This pin monitors voltage drop over an external current sense resistor RSENSE. Power dissipation of the P-MOSFET will be limited when ISENSE exceeds the voltage drop limit set in the Current Sense Register.                                                                                                                                                                                                                                                                                                                                 |

| 9         | CCOMP           | Compensation capacitor. A compensation ceramic capacitor must be added between CCOMP and GND to increase chip stability. This capacitor provides a negative feedback for the operational amplifier and its value can be from 30pF to 1000pF.                                                                                                                                                                                                                                                                                                                        |

| 10        | NC              | Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | UNITS<br>PER REEL | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |  |

|--------------------------------|-----------------|-------------------|--------------------|----------------------|----------------|--|

| ISL25700FRUZ-T                 | GT              | 3000              | -40 to +125        | 10 Ld 2.1x1.6 µTQFN  | L10.2.1x1.6A   |  |

| ISL25700FRUZ-TK                | GT              | 1000              | -40 to +125        | 10 Ld 2.1x1.6 µTQFN  | L10.2.1x1.6A   |  |

| ISL25700FRUZ-T7A               | GT              | 250               | -40 to +125        | 10 Ld 2.1x1.6 µTQFN  | L10.2.1x1.6A   |  |

NOTES:

1. Please refer to  $\underline{TB347}$  for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL25700</u>. For more information on MSL please see techbrief <u>TB363</u>.

#### **Absolute Maximum Ratings**

| Voltage at any Digital Interface Pin |  |

|--------------------------------------|--|

| with respect to CND                  |  |

| with respect to GND. | 0.3V to 6V      |

|----------------------|-----------------|

| V <sub>DD</sub>      | -0.3V to +16.5V |

| ESD Rating           |                 |

| Human Body Model (Tested per JESD22-A114F) | . 5kV |

|--------------------------------------------|-------|

| Machine Model (Tested per JESD22-A115B)    | 200V  |

| Latchup                                    | .25°C |

#### **Thermal Information**

| Thermal Resistance (Typical)      | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------|----------------------|------------------------|

| 10 Ld µTQFN Package (Note 4, 5)   | . 135                | 75                     |

| Storage Temperature               | 65°                  | 'C to +150°C           |

| Maximum Junction Temperature (Pla | stic Package         | ) +150°C               |

| Pb-Free Reflow Profile            | S                    | ee link below          |

| http://www.intersil.com/pbfree/Pb | -FreeReflow.         | asp                    |

#### **Recommended Operating Conditions**

Temperature Range (Full-range Industrial) .... -40°C to +125°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 5. For  $\theta_{JC}$  the "case temp" location is the center on the top of package.

#### **Analog Specifications** Over recommended operating conditions unless otherwise stated. **Boldface limits apply over** the operating temperature range, -40°C to +125°C.

| SYMBOL                                | MBOL PARAMETER TEST CONDITIONS                 |                                                                            |         | MIN<br>(Note 13) | TYP<br>(Note 6)       | MAX<br>(Note 13) | UNITS           |

|---------------------------------------|------------------------------------------------|----------------------------------------------------------------------------|---------|------------------|-----------------------|------------------|-----------------|

| T <sub>SET</sub>                      | Temperature Set Point                          | T <sub>SET</sub> must be above MIN                                         |         |                  | 40                    |                  | °C              |

|                                       |                                                | ambient                                                                    | MAX     |                  | 110                   |                  | °C              |

|                                       | Temperature Set Point Accuracy                 | 3 sigma standard deviation                                                 | on      |                  | ±3                    |                  | °C              |

| T <sub>SET_COARSE</sub>               | Coarse Adjustment of Set Point                 | R <sub>TH</sub> = 100k @ +25°C,<br>B <sub>25/85</sub> = 4100k (Note 14     |         | 15               |                       | °C               |                 |

| T <sub>SET_FINE</sub>                 | Fine Adjustment of Set Point                   |                                                                            |         |                  | 0.1                   |                  | °C              |

| T <sub>SET_FINE_INL</sub><br>(Note 9) | Fine Control Integral<br>Non-linearity         |                                                                            |         | -2.5             | ±0.9                  | +2.5             | LSB<br>(Note 7) |

| T <sub>SET_FINE_DNL</sub><br>(Note 8) | Fine Control Differential<br>Non-linearity     |                                                                            | -2      | ±0.5             | +2                    | LSB<br>(Note 7)  |                 |

| T <sub>DRIFT</sub>                    | Long-term Drift of Set Point                   | 1000h, Reg.1 = x2h, Reg.<br>Reg.3 = 90h                                    |         | ±0.5             |                       | °C               |                 |

| I <sub>TH</sub>                       | Thermistor Current Range                       |                                                                            | 25      | 40               | 55                    | μA               |                 |

| R <sub>TH</sub>                       | NTC Thermistor Range                           | Resistance @ +25°C                                                         |         | 20               | 100                   | 200              | kΩ              |

| V <sub>OUT</sub>                      | External P-MOSFET Gate Voltage                 | I <sub>OUT</sub> = 0μA                                                     |         | 0.25             |                       | V <sub>DD</sub>  | V               |

|                                       | V <sub>OUT</sub> Swing @ Fixed V <sub>DD</sub> | I <sub>OUT</sub> = 0μA                                                     | MIN     |                  | V <sub>DD</sub> - 2.5 |                  | V               |

| I <sub>OUT</sub>                      | Output Current                                 |                                                                            |         |                  |                       | 7                | μA              |

| V <sub>SENSE</sub>                    | Overcurrent Protection Set Point               | V <sub>SENSE</sub> = I <sub>SENSE</sub> × R <sub>SENS</sub><br>see Table 3 | se;     |                  | 200 to 1750           |                  | mV              |

| GENERAL PU                            | RPOSE DAC (MEASUREMENT                         | S BETWEEN GND AND V                                                        | DAC)    |                  |                       |                  |                 |

| V <sub>DAC MAX</sub>                  | Maximum DAC Output                             | Using internal V <sub>REF</sub> , V <sub>DD</sub><br>load, Gain = 1        | ≤5V, No |                  | 2                     | 2.5              | V               |

|                                       |                                                | $V_{DD} > 5V$ , No load, Gain = 2                                          |         |                  | 4                     | 5.0              | V               |

| INL<br>(Note 9)                       | Integral Non-Linearity                         | No load                                                                    | -1      | ±0.4             | +1                    | LSB<br>(Note 7)  |                 |

| DNL<br>(Note 8)                       | Differential Non-linearity                     | No load                                                                    |         | -0.75            | ±0.3                  | +0.75            | LSB<br>(Note 7) |

# Analog Specifications Over recommended operating conditions unless otherwise stated. Boldface limits apply over the operating temperature range, -40°C to +125°C. (Continued)

| SYMBOL                               | PARAMETER                    | TEST CONDITIONS                                     | MIN<br>(Note 13) | TYP<br>(Note 6) | MAX<br>(Note 13) | UNITS           |

|--------------------------------------|------------------------------|-----------------------------------------------------|------------------|-----------------|------------------|-----------------|

| V <sub>DAC_OFFSET</sub>              | Offset                       | DAC register set to 0, No load                      | 0                | 0.2             | 1                | LSB<br>(Note 7) |

| R <sub>OUT</sub>                     | DAC Output Impedance         |                                                     |                  | 350             |                  | Ω               |

| PSRR                                 | Power Supply Rejection Ratio | DAC at middle scale, frequency<br>from 0Hz to 25kHz |                  | -85             |                  | dB              |

| TC <sub>V</sub><br>(Notes 10,<br>11) | Temperature Coefficient      | DAC register set between 20 hex<br>and FF hex       |                  | ±45             |                  | ppm/°C          |

# **Operating Specifications** Over the recommended operating conditions unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +125°C.

| SYMBOL                        | PARAMETER                                                   | TEST CONDITIONS                                                                                                                  | MIN<br>(Note 13)      | TYP<br>(Note 6) | MAX<br>(Note 13) | UNITS  |

|-------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|------------------|--------|

| I <sub>DD1</sub>              | V <sub>DD</sub> Supply Current<br>(Non-Volatile Write/read) | $f_{SCL} = 400$ kHz; SDA = Open;<br>(for I <sup>2</sup> C, Active, Read and Write<br>States) I <sub>PMOS</sub> = 0mA, DAC unload |                       |                 | 4                | mA     |

| I <sub>DD2</sub>              | V <sub>DD</sub> Supply Current<br>(Volatile Write/read)     | $I_{PMOS} = 0mA$ , DAC unload                                                                                                    |                       |                 | 2.8              | mA     |

| I <sub>LkgDig</sub>           | Leakage Current, at SDA and SCL Pins                        | Voltage at pin from GND to VCC                                                                                                   | -2                    |                 | 2                | μA     |

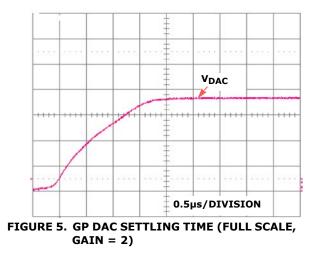

| t <sub>DAC</sub><br>(Note 11) | DAC Settling Time                                           | From bus STOP condition to V <sub>DAC</sub> change                                                                               |                       |                 | 3                | μs     |

| V <sub>POR</sub>              | Power-On Recall Voltage                                     | Minimum V <sub>DD</sub> at which memory recall occurs                                                                            |                       | 2.5             | 2.9              | V      |

| V <sub>DD</sub> Ramp          | V <sub>DD</sub> Ramp Rate                                   | @ any level from 0V to 15V                                                                                                       | 0.2                   |                 | 50               | V/ms   |

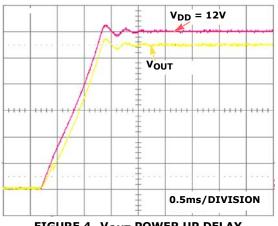

| t <sub>D</sub><br>(Note 11)   | Power-Up Delay                                              | $V_{DD}$ above $V_{POR}$ , to DAC Register recall completed, and I <sup>2</sup> C Interface in standby state                     |                       | 1               | ms               |        |

| EEPROM S                      | PECIFICATIONS                                               |                                                                                                                                  |                       |                 |                  |        |

|                               | EEPROM Endurance                                            |                                                                                                                                  | 10,000                |                 |                  | Cycles |

|                               | EEPROM Retention                                            | Temperature ≤ +55°C                                                                                                              | 50                    |                 |                  | Years  |

|                               |                                                             | Temperature ≤ +125°C                                                                                                             | 10                    |                 |                  | Years  |

| SERIAL IN                     | TERFACE SPECIFICATIONS                                      |                                                                                                                                  |                       |                 |                  |        |

| V <sub>I2C</sub>              | I <sup>2</sup> C Bus Voltage                                | $V_{I2C} \leq V_{DD}$                                                                                                            | 2.7                   |                 | 5.5              | V      |

| $V_{\text{IL}}$               | SDA, and SCL Input Buffer LOW Voltage                       | $V_{I2C}$ from 2.7V to 5.5V                                                                                                      |                       |                 | 0.8              | V      |

| $V_{\mathrm{IH}}$             | SDA, and SCL Input Buffer<br>HIGH Voltage                   | $V_{I2C}$ from 2.7V to 5.5V                                                                                                      | 1.4                   |                 |                  | V      |

| Hysteresis<br>(Note 11)       | SDA and SCL Input Buffer<br>Hysteresis                      |                                                                                                                                  | 0.05*V <sub>I2C</sub> |                 |                  | V      |

| V <sub>OL</sub><br>(Note 11)  | SDA Output Buffer LOW<br>Voltage, Sinking 4mA               |                                                                                                                                  | 0                     |                 | 0.4              | V      |

| Cpin<br>(Note 11)             | SDA, and SCL Pin Capacitance                                |                                                                                                                                  |                       |                 | 10               | pF     |

| f <sub>SCL</sub>              | SCL Frequency                                               |                                                                                                                                  |                       |                 | 400              | kHz    |

| t <sub>IN</sub><br>(Note 11)  | Pulse Width Suppression Time at SDA and SCL Inputs          | Any pulse narrower than the max spec is suppressed                                                                               |                       |                 | 50               | ns     |

| <b>Operating Specifications</b> | Over the recommended operating conditions unless otherwise specified. Boldface limits        |

|---------------------------------|----------------------------------------------------------------------------------------------|

|                                 | apply over the operating temperature range, $-40^{\circ}$ C to $+125^{\circ}$ C. (Continued) |

| SYMBOL                               | PARAMETER                                                              | TEST CONDITIONS                                                                                                                                                                                                                                            | MIN<br>(Note 13) | TYP<br>(Note 6) | MAX<br>(Note 13) | UNITS |

|--------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|-------|

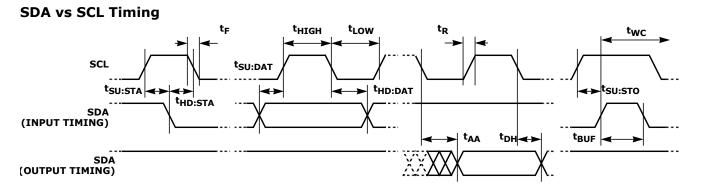

| t <sub>AA</sub><br>(Note 11)         | SCL Falling Edge to SDA<br>Output Data Valid                           | SCL falling edge crossing 30% of $V_{I2C},$ until SDA exits the 30% to 70% of $V_{I2C}$ window                                                                                                                                                             |                  |                 | 900              | ns    |

| t <sub>BUF</sub><br>(Note 11)        | Time the Bus Must be Free<br>Before the Start of a New<br>Transmission | SDA crossing 70% of $V_{I2C}$ during a STOP condition, to SDA crossing 70% of $V_{I2C}$ during the following START condition                                                                                                                               | 1300             |                 |                  | ns    |

| t <sub>LOW</sub>                     | Clock LOW Time                                                         | Measured at the 30% of $V_{\mbox{I2C}}$ crossing                                                                                                                                                                                                           | 1300             |                 |                  | ns    |

| t <sub>HIGH</sub>                    | Clock HIGH Time                                                        | Measured at the 70% of $V_{I2C}$ crossing                                                                                                                                                                                                                  | 600              |                 |                  | ns    |

| t <sub>SU:STA</sub>                  | START Condition Setup Time                                             | SCL rising edge to SDA falling edge.<br>Both crossing 70% of V <sub>I2C</sub> .                                                                                                                                                                            | 600              |                 |                  | ns    |

| t <sub>HD:STA</sub>                  | START Condition Hold Time                                              | From SDA falling edge crossing 30% of V_{I2C} to SCL falling edge crossing 70% of V_{I2C}                                                                                                                                                                  | 600              |                 |                  | ns    |

| t <sub>SU:DAT</sub>                  | Input Data Setup Time                                                  | From SDA exiting the 30% to 70% of $V_{I2C}$ window, to SCL rising edge crossing 30% of $V_{I2C}$                                                                                                                                                          | 100              |                 |                  | ns    |

| t <sub>HD:DAT</sub>                  | Input Data Hold Time                                                   | From SCL falling edge crossing 70% of $V_{I2C}$ to SDA entering the 30% to 70% of $V_{I2C}$ window                                                                                                                                                         | 0                |                 |                  | ns    |

| t <sub>SU:STO</sub>                  | STOP Condition Setup Time                                              | From SCL rising edge crossing 70% of $V_{I2C}$ to SDA rising edge crossing 30% of $V_{I2C}$                                                                                                                                                                | 600              |                 |                  | ns    |

| t <sub>DH</sub>                      | Output Data Hold Time                                                  | From SCL falling edge crossing 30% of $V_{I2C}$ , until SDA enters the 30% to 70% of $V_{I2C}$ window                                                                                                                                                      | 0                |                 |                  | ns    |

| t <sub>R</sub>                       | SDA and SCL Rise Time                                                  | From 30% to 70% of $V_{I2C}$                                                                                                                                                                                                                               | 20 +<br>0.1 * Cb |                 | 250              | ns    |

| t <sub>F</sub>                       | SDA and SCL Fall Time                                                  | From 70% to 30% of $V_{\rm I2C}$                                                                                                                                                                                                                           | 20 +<br>0.1 * Cb |                 | 250              | ns    |

| Cb                                   | Capacitive Loading of SDA or SCL                                       | Total on-chip and off-chip                                                                                                                                                                                                                                 | 10               |                 | 400              | pF    |

| Rpu<br>(Note 11)                     | SDA and SCL Bus Pull-Up<br>Resistor Off-Chip                           | $\begin{array}{l} \mbox{Maximum is determined by } t_R \mbox{ and } t_F. \\ \mbox{For Cb} = 400 \mbox{pF}, \mbox{ max is about } 2{\sim}2.5 \mbox{k}\Omega. \\ \mbox{For Cb} = 40 \mbox{pF}, \mbox{ max is about } 15{\sim}20 \mbox{k}\Omega. \end{array}$ | 1                |                 |                  | kΩ    |

| t <sub>WC</sub><br>(Notes<br>11, 12) | Non-Volatile Write Cycle Time                                          |                                                                                                                                                                                                                                                            |                  | 15              | 20               | ms    |

NOTES:

- 6. Typical values are for  $T_A = +25^{\circ}C$  and 12V supply voltage.

- 7. LSB: [VDAC255 VDAC0]/255. VDAC255 and VDAC0 are the DAC output voltage when DAC register set to FF hex and 00 hex respectively.

- 8. DNL =  $[VDAC_i VDAC_{i-1}]/LSB-1$ , for i = 1 to 255. i is the DAC register setting.

- 9. INL =  $[VDAC_i (i \cdot LSB + VDAC_0)]/LSB$  for i = 1 to 255. 10.  $TC_V = \frac{VDAC_i(T) VDAC_i(40^{\circ}C)}{VDAC_i(40^{\circ}C)} \times \frac{10^6}{(T 40)^{\circ}C}$  for i = 1 to 255 decimal, T = -40°C to +125°C, referenced to 40°C. 10.

- 11. Limits established by characterization and are not production tested.

- 12.  $t_{WC}$  is the time from a valid STOP condition at the end of a Write sequence of a I<sup>2</sup>C serial interface Write operation, to the end of the self-timed internal non-volatile write cycle. The Busy Polling method can be used to determine the end of the non-volatile write cycle.

- 13. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 14. B<sub>25/85</sub> is a thermistor material specific constant; represents the slope of the Resistance vs. Temperature curve.

### **Typical Performance Curves**

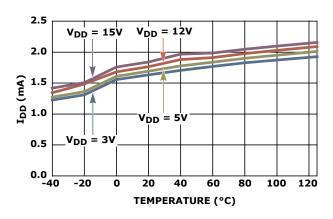

FIGURE 2. SUPPLY CURRENT IDD vs VDD

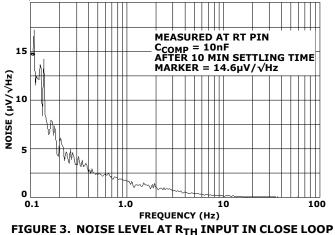

APPLICATION  $2\mu V/\sqrt{Hz} @ 1Hz$

### Typical Performance Curves (Continued)

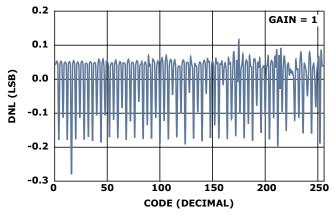

FIGURE 6. GP DAC DNL vs CODE  $V_{DD} = 3V$

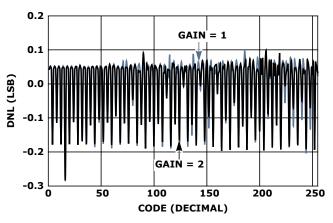

FIGURE 7. GP DAC DNL vs CODE  $V_{DD}$  = 5V

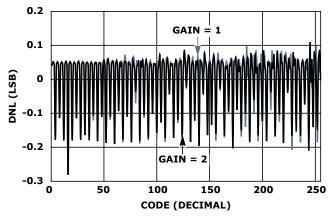

FIGURE 8. GP DAC DNL vs CODE  $V_{DD} = 15V$

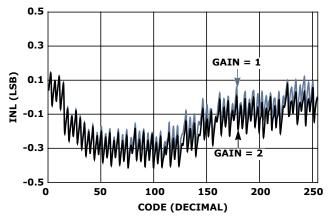

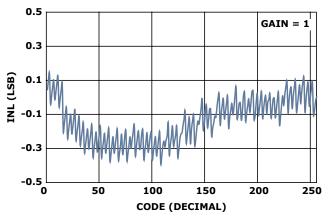

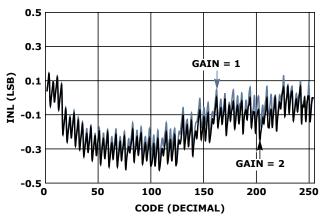

FIGURE 10. GP DAC INL vs CODE  $V_{DD} = 5V$

FIGURE 9. GP DAC INL vs CODE  $V_{DD}$  = 3V

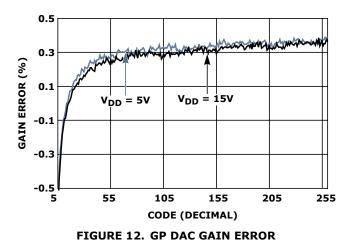

### **Typical Performance Curves** (Continued)

### **Principles of Operation**

The ISL25700 allows for precisely controlling the temperature of an external object and/or power dissipation of the external P-MOSFET. The temperature control is done by continuously sensing resistance of the NTC thermistor, and adjusting the current flow through the P-MOSFET (temperature controlling element).

ISL25700 drives the P-MOSFET proportionally inverted to the difference between the object temperature and target temperature set point ( $T_{SET}$ ), set by the user through the I<sup>2</sup>C serial interface. Temperature is sensed by the external NTC thermistor and converted to a driving voltage by the Wheatstone bridge and its amplifier. One leg of the current-mode Wheatstone bridge contains an external NTC thermistor with the programmable 8-bit FTC DAC and another leg contains the selectable current source K1 that feeds an internal resistor R<sub>INT</sub>.

The 8-bit FTC DAC allows fine-tuning the T<sub>SET</sub> with resolution better than +0.1°C within a +15°C coarse temperature range window. The T<sub>SET</sub> temperature is set through the Temperature Coarse Range Control Register, Reg.01h[2:0], and the Fine Temperature Control Register, Reg.02h[7:0]; refer to "ISL25700 MEMORY MAP" on page 11. A +15°C temperature coarse range window can be centered on T<sub>SET</sub> point based on the thermistor's parameters, such as resistance, R/T curve type, tolerance and NTC slope and by adjusting a current ratio flowing through the legs of the Wheatstone bridge. Note that the T<sub>SET</sub> target temperature should be higher than the anticipated maximum ambient temperature for the application.

There are total of 32 system gain settings available in the Gain Control Register, Reg.03h[4:0], with 0.35dB resolution per step. The gain control allows to prevent the thermal system from oscillation by adjusting the total system gain remotely, without use of external components. The internal current sensing circuitry provides the ability to control and adjust the power dissipated in the P-MOSFET through the Current Sense Register, Reg.01h[7:3]. This function allows for adjusting the initial turn on heating curve and protects from over-heating of the P-MOSFET. An external current sensing resistor R<sub>SENSE</sub>, serial with the P-MOSFET, is required. A current limit can be selected for the chosen R<sub>SENSE</sub>. It should have an effective voltage drop from 200mV to 1750mV and be inside the safe operating area of the MOSFET.

A General Purpose 8-bit DAC, GP DAC provides a programmable voltage output  $V_{DAC}$  through the General Purpose DAC Register, Reg.04h[7:0]. The output swing of General Purpose DAC can be set through the Gain Control bit in Reg.03h[6] or totally disabled by resetting the DAC Enable Bit in Reg.03h[7].

#### **Memory Map**

The are two types of memory banks in the chip; volatile (RAM) and non-volatile (EEPROM). Volatile registers from address 00h to 07h are identical to non-volatile registers in terms of the register's name and bit definitions. All the data is recalled from non-volatile registers and maintained in the volatile registers at power-up. It is possible to do independent write/read to the volatile and non-volatile banks after power-up by setting NV bit in the Control/Status Register, Reg.08h[7]. Note that the data written to the non-volatile registers will be automatically written to corresponding volatile registers, however no direct reading from non-volatile registers is possible. All the readings are from corresponding volatile registers.

The Memory Map of the chip is in Table 1.

|                                                         | REGISTER |               |             |        | BIT    | МАР    |        |        |        | DEFAULT  |

|---------------------------------------------------------|----------|---------------|-------------|--------|--------|--------|--------|--------|--------|----------|

| REGISTER NAME                                           | ADDRESS  | 7             | 6           | 5      | 4      | 3      | 2      | 1      | 0      | SETTINGS |

| Device ID (Read Only)                                   | 00h      | ID[7]         | ID[6]       | ID[5]  | ID[4]  | ID[3]  | ID[2]  | ID[1]  | ID[0]  | 00h      |

| Current Sense/<br>Coarse Temperature Control            | 01h      | CS[4]         | CS[3]       | CS[2]  | CS[1]  | CS[0]  | CTC[2] | CTC[1] | CTC[0] | 03h      |

| Fine Temperature Control                                | 02h      | FTC[7]        | FTC[6]      | FTC[5] | FTC[4] | FTC[3] | FTC[2] | FTC[1] | FTC[0] | 80h      |

| Gain Control (DAC Enable/<br>DAC Gain/System Loop Gain) | 03h      | DAC<br>Enable | DAC<br>Gain | NA     | SLG[4] | SLG[3] | SLG[2] | SLG[1] | SLG[0] | 90h      |

| General Purpose DAC                                     | 04h      | DAC[7]        | DAC[6]      | DAC[5] | DAC[4] | DAC[3] | DAC[2] | DAC[1] | DAC[0] | 80h      |

| General Purpose Register 1                              | 05h      | GP1[7]        | GP1[6]      | GP1[5] | GP1[4] | GP1[3] | GP1[2] | GP1[1] | GP1[0] | 00h      |

| General Purpose Register 2                              | 06h      | GP2[7]        | GP2[6]      | GP2[5] | GP2[4] | GP2[3] | GP2[2] | GP2[1] | GP2[0] | 00h      |

| R <sub>INT</sub> Absolute Error (Read Only)             | 07h      | sign bit      | ERR[6]      | ERR[5] | ERR[4] | ERR[3] | ERR[2] | ERR[1] | ERR[0] | XX       |

| Control/Status Register<br>(Volatile Only)              | 08h      | NV            | NA          | NA     | NA     | NA     | NA     | NA     | BUSY   | 00h      |

#### TABLE 1. ISL25700 MEMORY MAP

#### Device ID Register (Reg.00h)

This is a read only register. It contains device ID code 00h.

#### Coarse Temperature Control (Reg.01h [2:0])

These 3 bits allow one to choose one of the seven coarse windows for the temperature set point. The default set point is about +59°C for the 100k  $R_{TH}$  thermistor with a temperature coefficient of -4.25%/°C at +25°C, i.e. Reg.01h[2:0] = 011b. The temperature set point can be changed to any other set point within an operational range from +40°C to +110°C, or use another type of thermistor, including different resistance value or R/T curve type (NTC slope), and then center the +15°C coarse range temperature window on that new setting based on the ratio of  $R_{INT}/R_{TH}$  according to Equation 1:

$$\frac{\mathsf{R}_{\mathsf{INT}}(\mathsf{T})}{\mathsf{R}_{\mathsf{TH}}(\mathsf{setpoint})} = \frac{\mathsf{K2} + \mathsf{K3} \times \frac{\mathsf{Code}}{255}}{\mathsf{K1}} \tag{EQ. 1}$$

where:

$R_{INT}$  - is an internal  $9k\Omega$  resistor, forming another leg of the Wheatstone Bridge;

K1, K2 and K3 - are coefficients representing the ratio of the current flowing through the legs of the Wheatstone Bridge;

Code - is the decimal code in the Fine Temperature Control register 02h.

The value of internal resistor  $R_{INT}$  can vary from part to part and depends on the package temperature. The actual  $R_{INT}$  at temperature T can be calculated using Equation 2:

$$R_{INT}(T) = R_{INT}(25)x[1 + \alpha(T - 25) + \beta(T - 25)^{2}]$$

(EQ. 2)

where:

$R_{INT}(25) = 9000 + R_{INT}$  abs. error x 15 - is internal resistor value at +25°C in Ohms;

$\mathsf{R}_{\text{INT}}$  abs. error - is a signed integer value of absolute

error stored in Reg.07h[7:0] converted to a decimal number; bit [7] represents a sign bit, 0 for "+" and 1 for "-";

$\alpha$ = -1337×10<sup>-6</sup> - 1st order temperature coefficient, ppm/°C;

$\beta = 5 \times 10^{-6}$  - 2nd order temperature coefficient, ppm/°C<sup>2</sup>;

T - temperature in Celsius.

The K1, K2 and K3 coefficients and the thermistor value range for each Coarse Temperature setting in Reg.01h[2:0] should be taken according to Table 2.

| TABLE 2. COARSE TEMPERATURE RANG |

|----------------------------------|

|----------------------------------|

| Register<br>01h[2:0] | К1 | К2         | КЗ | THERMISTOR<br>RESISTANCE RANGE<br>AT SET POINT (kΩ) |  |

|----------------------|----|------------|----|-----------------------------------------------------|--|

| 000                  |    | Do not use |    |                                                     |  |

| 001                  | 3  | 3          | 2  | 5.4 to 9.0                                          |  |

| 010                  | 4  | 3          | 2  | 7.2 to 12.0                                         |  |

| 100                  | 5  | 3          | 2  | 9.0 to 15.0                                         |  |

| 011                  | 7  | 3          | 2  | 12.6 to 21.0                                        |  |

| 101                  | 8  | 3          | 2  | 14.4 to 24.0                                        |  |

| 110                  | 9  | 3          | 2  | 16.2 to 27.0                                        |  |

| 111                  | 12 | 3          | 2  | 21.6 to 36.0                                        |  |

#### Current Sense Threshold (Reg.01h [7:3])

This register sets the current limit trip point. When the voltage applied to the  $I_{\mbox{SENSE}}$  pin falls below the programmed voltage threshold,  $V_{\mbox{OUT}}$  goes high, thus forming a negative feedback loop proportional to  $I_{\mbox{SENSE}}$  x  $R_{\mbox{SENSE}}$ .

The value for this register should be taken according to Table 3.

#### TABLE 3. CURRENT SENSE THRESHOLD

| SENSE RESISTOR       |                                                              | TYPICAL ERROR (%)    |                       |  |  |

|----------------------|--------------------------------------------------------------|----------------------|-----------------------|--|--|

| Register<br>01h[7:3] | VOLTAGE DROP<br>THRESHOLD                                    |                      |                       |  |  |

| Value                | V <sub>DD</sub> - (I <sub>SENSE</sub> X R <sub>SENSE</sub> ) | V <sub>DD</sub> = 3V | V <sub>DD</sub> = 15V |  |  |

| 00000                | V <sub>DD</sub> - 200mV                                      | ±5                   | +20                   |  |  |

| 00001                | V <sub>DD</sub> - 250mV                                      | ±5                   | +20                   |  |  |

| 00010                | V <sub>DD</sub> - 300mV                                      | ±5                   | +20                   |  |  |

| 00011                | V <sub>DD</sub> - 350mV                                      | ±5                   | +20                   |  |  |

| 00100                | V <sub>DD</sub> - 400mV                                      | ±5                   | +20                   |  |  |

| 00101                | V <sub>DD</sub> - 450mV                                      | ±5                   | +20                   |  |  |

| 00110                | V <sub>DD</sub> - 500mV                                      | ±5                   | +20                   |  |  |

| 00111                | V <sub>DD</sub> - 550mV                                      | ±5                   | +20                   |  |  |

| 01000                | V <sub>DD</sub> - 600mV                                      | ±5                   | +20                   |  |  |

| 01001                | V <sub>DD</sub> - 650mV                                      | ±5                   | +20                   |  |  |

| 01010                | V <sub>DD</sub> - 700mV                                      | ±5                   | +20                   |  |  |

| 01011                | V <sub>DD</sub> - 750mV                                      | ±5                   | +20                   |  |  |

| 01100                | V <sub>DD</sub> - 800mV                                      | ±5                   | +20                   |  |  |

| 01101                | V <sub>DD</sub> - 850mV                                      | ±5                   | +20                   |  |  |

| 01110                | V <sub>DD</sub> - 900mV                                      | ±5                   | +20                   |  |  |

| 01111                | V <sub>DD</sub> - 950mV                                      | ±5                   | +20                   |  |  |

| 10000                | V <sub>DD</sub> - 1000mV                                     | ±5                   | +20                   |  |  |

| 10001                | V <sub>DD</sub> - 1050mV                                     | ±5                   | +20                   |  |  |

| 10010                | V <sub>DD</sub> - 1100mV                                     | ±5                   | +20                   |  |  |

| 10011                | V <sub>DD</sub> - 1150mV                                     | ±5                   | +20                   |  |  |

| 10100                | V <sub>DD</sub> - 1200mV                                     | ±5                   | +20                   |  |  |

| 10101                | V <sub>DD</sub> - 1250mV                                     | ±5                   | +20                   |  |  |

| 10110                | V <sub>DD</sub> - 1300mV                                     | ±5                   | +20                   |  |  |

| 10111                | V <sub>DD</sub> - 1350mV                                     | ±5                   | +20                   |  |  |

| 11000                | V <sub>DD</sub> - 1400mV                                     | ±5                   | +20                   |  |  |

| 11001                | V <sub>DD</sub> - 1450mV                                     | ±5                   | +20                   |  |  |

| 11010                | V <sub>DD</sub> - 1500mV                                     | ±5                   | +20                   |  |  |

| 11011                | V <sub>DD</sub> - 1550mV                                     | ±5                   | +20                   |  |  |

| 11100                | V <sub>DD</sub> - 1600mV                                     | ±5                   | +20                   |  |  |

| 11101                | V <sub>DD</sub> - 1650mV                                     | ±5                   | +20                   |  |  |

| 11110                | V <sub>DD</sub> - 1700mV                                     | ±5                   | +20                   |  |  |

| 11111                | V <sub>DD</sub> - 1750mV                                     | ±5                   | +20                   |  |  |

# Fine Temperature Control Register (Reg.02h [7:0])

This register allows fine tuning to the final temperature  $T_{SET}$  within the predetermined range set in Reg.01h[2:0] by choosing appropriate code for the 8-bit FTC DAC. The final temperature can be adjusted with approximately +0.07°C increment/decrement resolution per step.

#### System Loop Gain (Reg.03h [4:0])

This 5 bits allow one to adjust a total system loop gain in  $\pm 0.35$ dB per step, according to Table 4.

The default system loop gain depends on the MOSFET type, thermal conductivity and level of insulation from the ambient temperature.

#### TABLE 4. SYSTEM LOOP GAIN ADJUSTMENT

| 00000         -5.60           00010         -5.25           00010         -4.90           00011         -4.55           00100         -4.20           00101         -3.85           00110         -3.85           00111         -3.15           01000         -2.80           01011         -2.45           01001         -2.45           01010         -2.10           01011         -1.75           01100         -1.40           01111         -0.35           01100         -1.40           01111         -0.35           01100         0.70           01111         -0.35           10000         Initial Gain (default)           10001         0.35           10010         0.70           10111         1.05           10010         1.40           10101         1.75           10100         1.40           10101         1.75           10100         2.10           10111         2.45           11000         2.80           11001         3.15           110                            | Reg.03h[4:0] | LOOP GAIN ADJUSTMENT   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------|

| 00001-5.2500010-4.9000011-4.5500100-4.2000101-3.8500100-3.5000111-3.1501000-2.8001001-2.4501010-2.1001011-1.75011001.4001011-1.05011010.7001111-0.3510000Initial Gain (default)100110.35100100.70101111.05100101.40100111.75101001.40101112.10101102.10101113.15110002.80110013.50110113.85111013.85111014.20111014.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _            | (dB)                   |

| 00010-4.9000011-4.5500100-4.2000101-3.8500101-3.5000111-3.1501000-2.8001001-2.4501001-2.1001011-1.7501100-1.4001011-1.05011000.7001111-0.3510000Initial Gain (default)100110.35100001.40101111.05101001.40101111.75101102.10101112.45110002.80110013.50110103.50110113.85111004.20111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                        |

| 00011         -4.55           00100         -4.20           00101         -3.85           00110         -3.50           00111         -3.15           01000         -2.80           01001         -2.45           01010         -2.10           01011         -1.75           01100         -1.40           01101         -1.05           01101         -0.70           01111         -0.35           10000         Initial Gain (default)           10011         1.05           10001         0.70           01111         -0.35           10000         Initial Gain (default)           10011         1.05           10010         0.70           10111         1.05           10010         1.40           10101         1.75           10101         1.75           10110         2.10           10111         2.45           11000         2.80           11001         3.15           11001         3.50           11011         3.85           11010         4.20                            | 00001        | -5.25                  |

| 00100         -4.20           00101         -3.85           00110         -3.50           00111         -3.15           01000         -2.80           01001         -2.45           01010         -2.10           01011         -1.75           01100         -1.40           01101         -1.05           01100         -1.40           01101         -0.70           01111         -0.35           01010         0.35           01011         1.05           01111         0.35           10000         Initial Gain (default)           10011         1.05           10010         0.70           10011         1.75           10010         1.40           10011         1.75           10100         1.40           10111         2.45           11010         3.15           11010         3.15           11001         3.50           11011         3.85           11001         4.20           11101         4.55           11101         4.90                                               | 00010        | -4.90                  |

| 00101         -3.85           00110         -3.50           00111         -3.15           01000         -2.80           01001         -2.45           01010         -2.10           01011         -1.75           01100         -1.40           01101         -1.05           01101         -0.70           01111         -0.35           10000         Initial Gain (default)           10011         0.35           10000         Initial Gain (default)           10011         1.05           10010         0.70           10011         1.75           10010         0.70           10011         1.05           10010         0.70           10011         1.40           10101         1.75           10100         2.10           10111         2.45           11000         2.80           11001         3.15           11001         3.50           11011         3.85           11001         4.20           11101         4.55           11101         4.90 <td>00011</td> <td>-4.55</td> | 00011        | -4.55                  |

| 00110         -3.50           00111         -3.15           01000         -2.80           01001         -2.45           01010         -2.10           01011         -1.75           01100         -1.40           01101         -1.05           01101         -1.05           01111         -0.35           01111         -0.35           01011         1.01           01111         0.35           10000         Initial Gain (default)           10011         0.35           10010         0.70           10011         1.05           10011         1.40           10011         1.40           10011         1.40           10101         1.75           10101         1.40           10101         1.75           10110         2.10           10111         2.45           11000         3.15           11001         3.15           11001         3.50           11101         3.85           11100         4.20           11101         4.55           111101 <td>00100</td> <td>-4.20</td>  | 00100        | -4.20                  |

| 00111-3.1501000-2.8001001-2.4501010-2.1001011-1.7501100-1.4001101-1.05011010.7001111-0.3510000Initial Gain (default)100110.35100100.70100111.05101011.75101102.10101112.45110013.15110013.50110103.50110113.85111004.20111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00101        | -3.85                  |

| 01000-2.8001001-2.4501010-2.1001011-1.7501100-1.4001101-1.0501101-0.7001111-0.3510000Initial Gain (default)100010.70100111.05100101.40100111.75101102.10101112.45110002.80110013.15110103.50110113.85110104.20111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00110        | -3.50                  |

| 01001-2.4501010-2.1001011-1.7501100-1.4001101-1.0501101-0.7001111-0.3510000Initial Gain (default)100010.35100100.70100111.05101001.40101011.75101102.10101112.45110002.80110013.15110103.50110113.85110104.20111104.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00111        | -3.15                  |

| 01010-2.1001011-1.7501100-1.4001101-1.0501101-0.7001111-0.3510000Initial Gain (default)100010.35100100.70100111.05101001.40101011.75101002.10101102.10101112.45110003.15110103.50110113.85111014.20111014.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01000        | -2.80                  |

| 01011-1.7501100-1.4001101-1.0501101-1.0501110-0.7001111-0.3510000Initial Gain (default)100010.70100100.70100111.05101001.40101011.75101002.10101112.45110002.80110013.15110103.50110113.85110104.20111014.55111004.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01001        | -2.45                  |

| 01100         -1.40           01101         -1.05           01101         -0.70           01111         -0.35           10000         Initial Gain (default)           10001         0.35           10010         0.70           10011         1.05           10010         0.70           10011         1.05           10100         1.40           10111         1.05           10100         1.40           10101         1.75           10110         2.10           10111         2.45           11000         2.80           11001         3.15           11001         3.50           11011         3.85           11010         4.20           11101         4.55           11101         4.90                                                                                                                                                                                                                                                                                                | 01010        | -2.10                  |

| 01101-1.0501110-0.7001111-0.3510000Initial Gain (default)100010.35100100.70100111.05101001.40101011.75101102.10101112.45110002.80110013.15110103.50110113.85111014.20111014.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 01011        | -1.75                  |

| 01110-0.7001111-0.3510000Initial Gain (default)100010.35100100.70100111.05101001.40101011.75101102.10101112.45110002.80110013.15110103.50110113.85111014.20111014.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01100        | -1.40                  |

| 01111         -0.35           10000         Initial Gain (default)           10001         0.35           10010         0.70           10011         1.05           10100         1.40           10101         1.75           10101         2.10           10111         2.45           11000         2.80           11001         3.15           11001         3.50           11011         3.85           11101         4.55           11101         4.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 01101        | -1.05                  |

| 10000         Initial Gain (default)           10001         0.35           10010         0.70           10011         1.05           10100         1.40           10101         1.75           10110         2.10           10111         2.45           11000         2.80           11001         3.15           11010         3.50           11011         3.85           11100         4.20           11101         4.55           11110         4.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 01110        | -0.70                  |

| 100010.35100100.70100111.05101001.40101011.75101102.10101112.45110002.80110013.15110103.50110113.85111014.20111014.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 01111        | -0.35                  |

| 100100.70100111.05101001.40101011.75101102.10101112.45110002.80110013.15110103.50110113.85111004.20111014.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10000        | Initial Gain (default) |

| 100111.05101001.40101011.75101102.10101112.45110002.80110013.15110103.50110113.85111014.20111014.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10001        | 0.35                   |

| 10100         1.40           10101         1.75           10110         2.10           10111         2.45           11000         2.80           11001         3.15           11010         3.50           11011         3.85           11100         4.20           11101         4.55           11110         4.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10010        | 0.70                   |

| 10101         1.75           10110         2.10           10111         2.45           11000         2.80           11001         3.15           11011         3.85           11100         4.20           11101         4.55           11110         4.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10011        | 1.05                   |

| 101102.10101112.45110002.80110013.15110103.50110113.85111004.20111014.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10100        | 1.40                   |

| 101112.45110002.80110013.15110103.50110113.85111004.20111014.55111104.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10101        | 1.75                   |

| 11000         2.80           11001         3.15           11010         3.50           11011         3.85           11100         4.20           11101         4.55           11110         4.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10110        | 2.10                   |

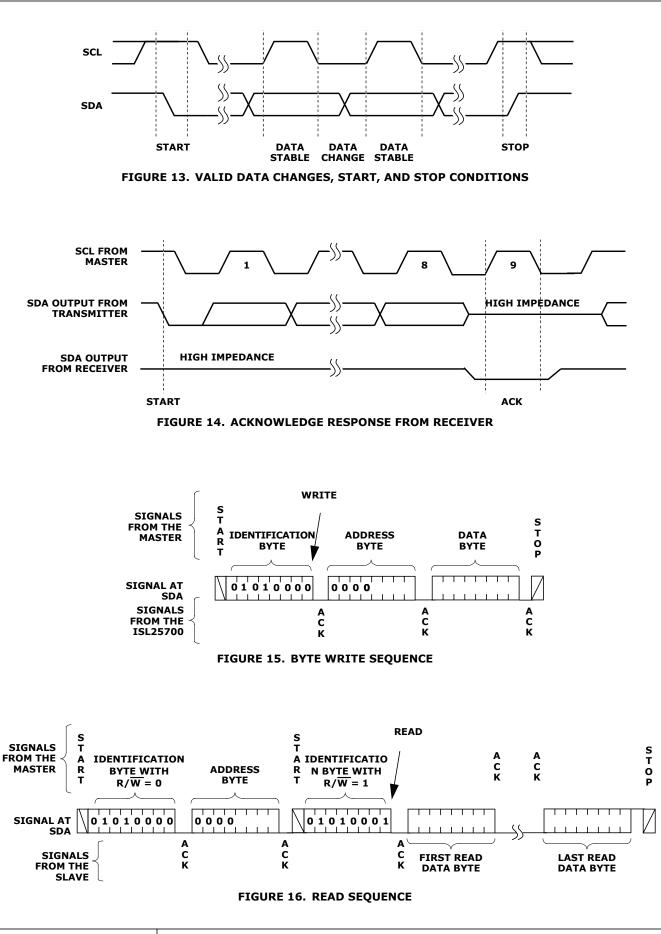

| 11001     3.15       11010     3.50       11011     3.85       11100     4.20       11101     4.55       11110     4.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10111        | 2.45                   |