# LCD segment driver BU9706KS

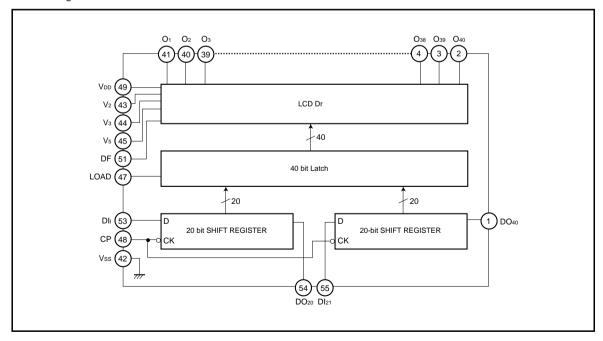

The BU9706KS is a 40-output LCD segment driver provided with a 40-bit shift register and a 40-bit latch.

As the 40-bit shift register can be divided into two 20-bit sections, it can be used efficiently, based on the number of segments and the character configuration.

Also, by using a number of BU9706KS drivers, it is possible to configure an LCD segment driver of more than 80 bits.

As the liquid crystal drive voltage can be set externally to any value, it can be used as a driver IC for both static and dynamic drive in various types of liquid crystal display panels.

#### Features

- 40-bit shift register and 40-bit latch enable serial input - parallel output.

- 2) Shift register can be divided into two 20-bit sections.

- 3) Power supply voltage: 3.5 to 6V.

- 4) LCD drive voltage: 3 to 6V.

- 5) Can accommodates duty of 1 / 8 to 1 / 16.

- 6) Can be used as a driver IC for static drive by setting the liquid crystal drive voltage externally (V3 = V<sub>DD</sub>, V2 = V5 = Vss, connect DF as LCD common).

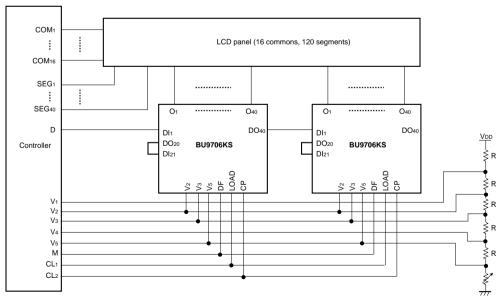

#### Block diagram

### ●Absolute maximum ratings (Ta = 25°C, Vss = 0V)

| Parameter                 | Symbol                           | Limits                | Unit |

|---------------------------|----------------------------------|-----------------------|------|

| Power supply voltage      | V <sub>DD</sub>                  | - 0.3 ~ <b>+</b> 6.5  | V    |

| LCD power supply voltage* | V <sub>DD</sub> – V <sub>5</sub> | 0 ~ + 6.5             | V    |

| Input voltage             | Vin                              | Vss - 0.3 ~ Vdd + 0.3 | V    |

| Power dissipation         | Pd                               | 500                   | mW   |

| Operating temperature     | Topr                             | - 20 ~ + 70           | °C   |

| Storage temperature       | Tstg                             | - 55 ~ + 125          | °C   |

<sup>\*</sup> The LCD power supply voltage must satisfy the condition of VDD >  $V2 \ge V3 > V5 \ge Vss$ .

# ●Recommended operating conditions (Ta = 25°C, Vss = 0V)

| Parameter                 | Symbol                           | Min. | Тур. | Max.            | Unit |

|---------------------------|----------------------------------|------|------|-----------------|------|

| Power supply voltage      | V <sub>DD</sub>                  | 3.5  | _    | 6.0             | V    |

| LCD power supply voltage* | V <sub>DD</sub> – V <sub>5</sub> | 3.0  | _    | 6.0             | V    |

| Input voltage             | Vin                              | 0    | _    | V <sub>DD</sub> | V    |

<sup>\*</sup> The LCD power supply voltage must satisfy the condition of VDD >  $V2 \ge V3 > V5 \ge Vss$ .

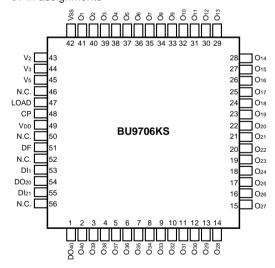

## Pin assignments

Standard ICs BU9706KS

### Pin descriptions

| Pin No. | Pin name                         | 1/0 | Function                                                                                                                                                                                                                                                                |  |  |  |  |  |

|---------|----------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2 ~ 41  | O <sub>40</sub> ~ O <sub>1</sub> | 0   | Output pin for the liquid crystal driver. $V_{DD}$ , $V_2$ , $V_3$ or $V_5$ is output depending on the latch content and the DF signal. Refer to the truth table for the output level.                                                                                  |  |  |  |  |  |

| 43 ~ 45 | V2 ~ V5                          | _   | Power supply pin for liquid crystal drive                                                                                                                                                                                                                               |  |  |  |  |  |

| 49      | V <sub>DD</sub>                  | _   | Logic power supply pin and liquid crystal drive power supply pin                                                                                                                                                                                                        |  |  |  |  |  |

| 42      | Vss                              | _   | Logic power supply pin                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 53      | DI <sub>1</sub>                  | I   | Data input pin for the shift register (1 to 20 bits). Data is read to the first bit of the shift register at the clock signal falling edge.                                                                                                                             |  |  |  |  |  |

| 54      | DO <sub>20</sub>                 | 0   | Data output pin for the shift register (1 to 20 bits). Data is output in synchronization with the clock signal falling edge. A 40-bit shift register is accomplished by connecting pins 54 and 55.                                                                      |  |  |  |  |  |

| 55      | DI <sub>21</sub>                 | I   | Data input pin for the shift register (21 to 40 bits). Data is read to the 21st bit of the shift register at the clock signal falling edge.                                                                                                                             |  |  |  |  |  |

| 1       | DO <sub>40</sub>                 | 0   | Data output pin for the shift register (21 to 40 bits). Data is output in synchronization with the clock signal falling edge. It is used to configure an LCD driver with more than 40 bits by connecting it to the DI pin of the BU9706KS at the next stage.            |  |  |  |  |  |

| 48      | СР                               | I   | Clock signal input pin for the shift register. The contents of the shift register are shifted by 1 bit only at the clock signal falling edge.                                                                                                                           |  |  |  |  |  |

| 47      | LOAD                             | I   | Latch signal input pin for the 40-bit latch. The contents of the shift register are transferred to $O_1$ to $O_{40}$ at LOAD = "H" and the data is latched at LOAD = "L". While LOAD = "L", the latched data is held even if the contents of the shift register change. |  |  |  |  |  |

| 51      | DF                               | I   | Input pin for the signal which produces AC for LCD drive.                                                                                                                                                                                                               |  |  |  |  |  |

## ●LCD drive output pin truth table

| Latch data | DF | On terminal voltage |

|------------|----|---------------------|

| Н          | Н  | V <sub>5</sub>      |

| Н          | L  | V <sub>DD</sub>     |

| L          | Н  | V <sub>3</sub>      |

| L          | L  | V <sub>2</sub>      |

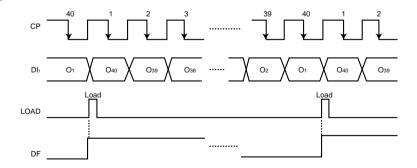

# ●Timing chart

- Shifted at CP input falling.

- When the LOAD input state becomes "H", the contents of the shift register are transferred to the segment outputs O1 to O40, and when it is "L", the data is latched.

Fig.1

Standard ICs BU9706KS

## ●Electrical characteristics (unless otherwise noted, Ta = 25°C, VDD = 5 V)

#### DC characteristics

| Parameter                   | Symbol | Min. | Тур. | Max. | Unit | Conditions                                   |

|-----------------------------|--------|------|------|------|------|----------------------------------------------|

| Input high level voltage*1  | ViH    | 4.0  | _    | _    | V    | _                                            |

| Input low level voltage*1   | VIL    | _    | _    | 1.0  | V    | _                                            |

| Input high level current*1  | Іін    | _    | _    | 1    | μΑ   | VIH = VDD                                    |

| Input low level current*1   | lı∟    | _    | _    | - 1  | μΑ   | VIL = 0V                                     |

| Output high level voltage*2 | Vон    | 4.2  | _    | _    | V    | Io = - 40μA                                  |

| Output low level voltage*2  | Vol    | _    | _    | 0.4  | V    | Io = 0.4mA                                   |

| ON resistance*3*4           | Ron    | _    | _    | 5    | kΩ   | V <sub>IN</sub> - V <sub>O</sub>  *5 = 0.25V |

| Current dissipation         | IDD    | _    | _    | 0.5  | mA   | CP = DC No load                              |

<sup>\*1</sup> Applied to DF, LOAD, CP, DI1 and DI21 pins

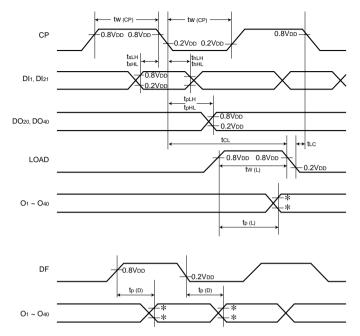

## AC characteristics

| Parameter                     | Symbol                     | Min. | Тур. | Max. | Unit | Conditions                       |

|-------------------------------|----------------------------|------|------|------|------|----------------------------------|

| Propagation delay time 1      | <b>t</b> pLH, <b>t</b> pHL | _    | _    | 250  | ns   | $CP \rightarrow DO_n$ delay time |

| Propagation delay time 2*     | tp (L)                     | _    | _    | 250  | ns   | Load → O <sub>n</sub> delay time |

| Propagation delay time 3*     | t <sub>p</sub> (D)         | _    | _    | 250  | ns   | $DF \rightarrow O_n$ delay time  |

| DI 	o CP setup time           | tslh, tshl                 | 50   | _    | _    | ns   | _                                |

| $CP \rightarrow DI$ hold time | thlm, thml                 | 50   | _    | _    | ns   | _                                |

| CP pulse width                | tw (CP)                    | 125  | _    | _    | ns   | _                                |

| Load pulse width              | tw (L)                     | 125  | _    | _    | ns   | _                                |

| CP 	o load time               | tcL                        | 250  | _    | _    | ns   | _                                |

| $LOAD \to CP$ time            | tLC                        | 0    | _    | _    | ns   | _                                |

| Maximum clock frequency       | <b>f</b> CP                | 3.3  | _    | _    | MHz  | DUTY = 50%                       |

VDD = 5V, V2 = 2 / 3VDD, V3 = 1 / 3VDD, V5 = 0V

<sup>\*2</sup> Applied to DO20 and DO40 pins

<sup>\*3</sup> Applied to O1 to O40 pins

$<sup>4 \</sup>text{ VDD} = 5 \text{ V}, \text{ V2} = 2 / 3 \text{ VDD}, \text{ V3} = 1 / 3 \text{ VDD}, \text{ V5} = 0 \text{ V}$

$<sup>\$5 \</sup>text{ VIN} = \text{VDD}, \text{ V2}, \text{ V3}, \text{ V5}, \text{ Vo} = \text{O}_n \text{ pin voltage}$

$<sup>\ \</sup>bigcirc$  Not designed for radiation resistance.

\*  $t_{p}$  (L) and  $t_{p}$  (D) are times required before the  $O_1$  to  $O_{40}$  output amplitude becomes 80% and 20% respectively.

Fig.2 AC characteristics waveform

# Application example

Fig.3

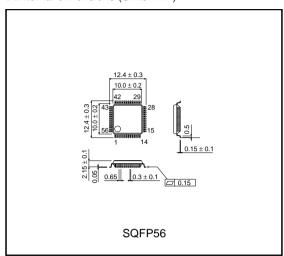

# ●External dimensions (Units: mm)

#### **Notes**

- No technical content pages of this document may be reproduced in any form or transmitted by any

means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the

product described in this document are for reference only. Upon actual use, therefore, please request

that specifications to be separately delivered.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard

use and operation. Please pay careful attention to the peripheral conditions when designing circuits

and deciding upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or

otherwise dispose of the same, no express or implied right or license to practice or commercially

exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document use silicon as a basic material.

Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

About Export Control Order in Japan

Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan.

In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.